Appearance

MAC简介

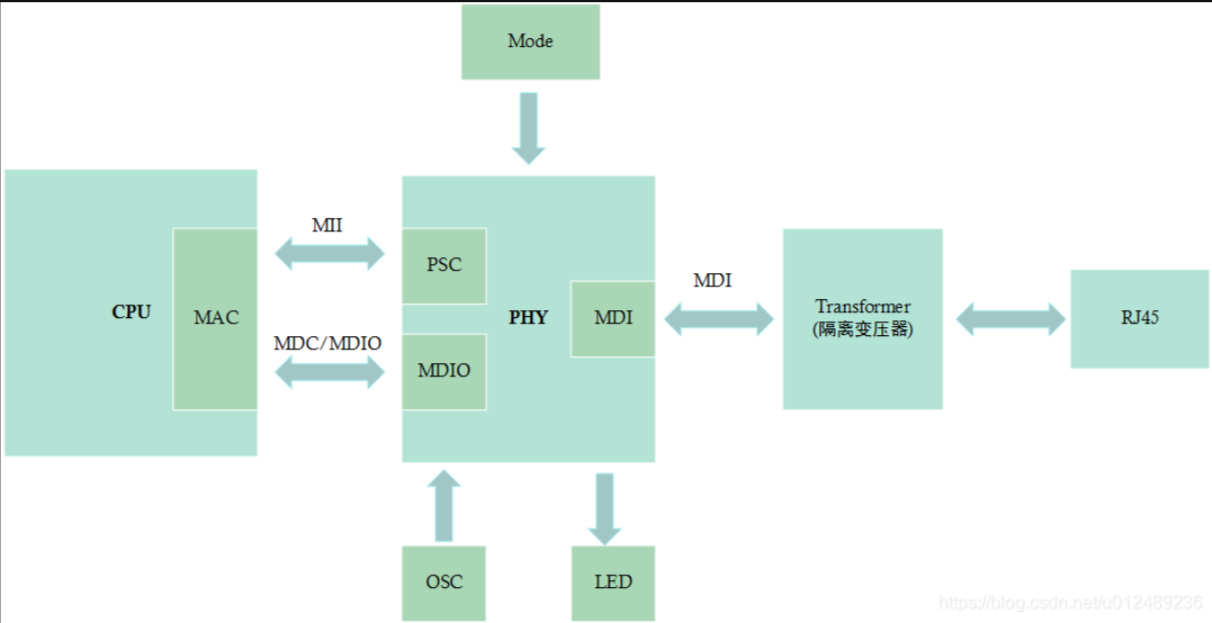

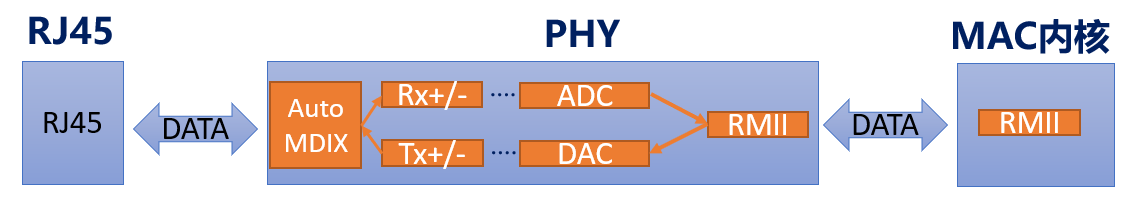

从硬件的角度来分析,以太网的电路接口一般由CPU、MAC(Media Access Control)控制器和物理层接口(physical Layer PHY)组成,如下图所示

对于上述三部分,并不一定都是独立的芯片,主要有以下几种情况

- CPU内部集成了MAC和PHY,难度较高

- CPU内部集成MAC,PHY采用独立芯片(主流方案)

- CPU不集成MAC和PHY,MAC和PHY采用独立芯片或者集成芯片(高端采用)

PHY整合了大量模拟硬件,而MAC是典型的全数字器件,芯片面积及模拟/数字混合架构是为什么先将MAC集成进微控制器而将PHY留在片外的原因。更灵活、密度更高的芯片技术已经可以实现MAC和PHY的单芯片整合

对于这种方案,其硬件方案比独立的相对于更简单,PHY与MAC之间有以下两个重要的硬件接口

- MDIO总线接口,主要是完成CPU对于PHY芯片的寄存器配置

- MII总线接口,主要是完成数据收发相关的业务

PHY实际的作用是把数据转换成可以发送出去的信号

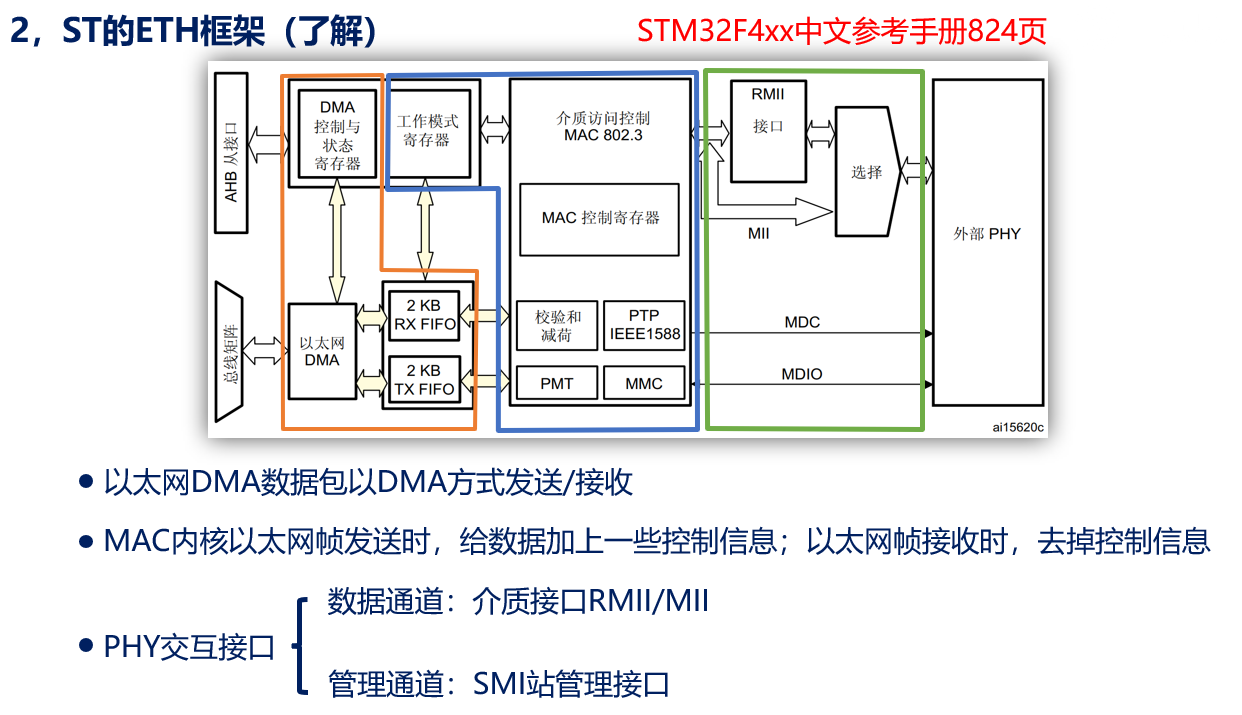

STM32实现

STM32里面自带有一个10/100Mbit/s的以太网MAC内核, 他提供地址以及媒体访问的控制方式

特性:

- 传输速率: 支持外部的PHY接口实现10/100Mbit/s的传输速率

- 协议标准: 符合IEEE802.3/3u的MII和RMII接口与以太网PHY通信

- 支持全双工以及半双工

- 支持通过MDIO接口配置以及管理PHY设备

MAC与PHY接口

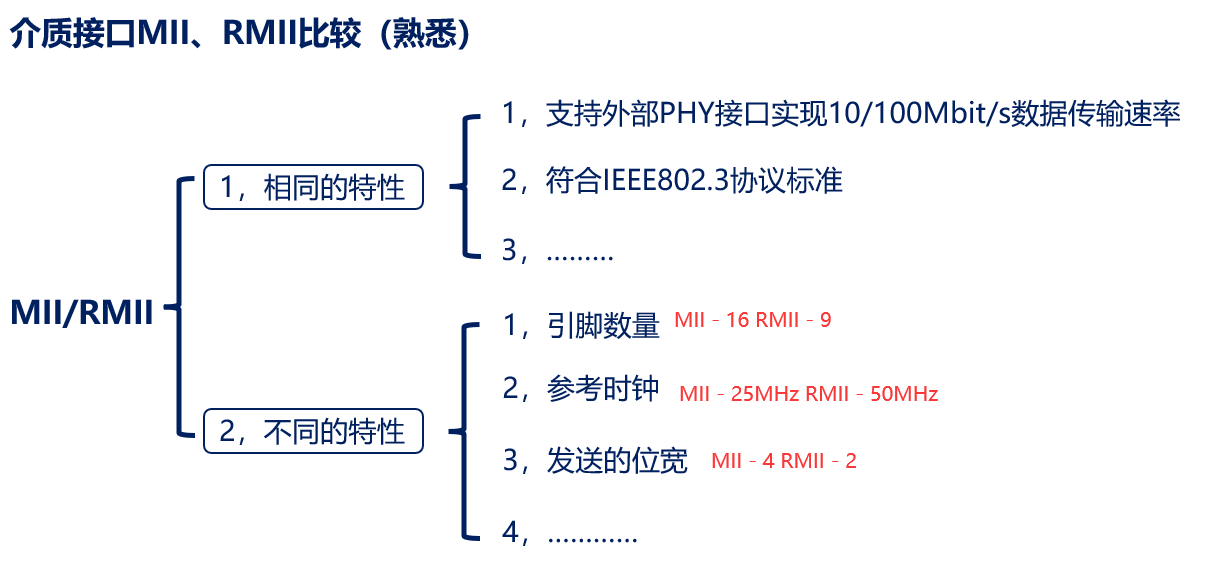

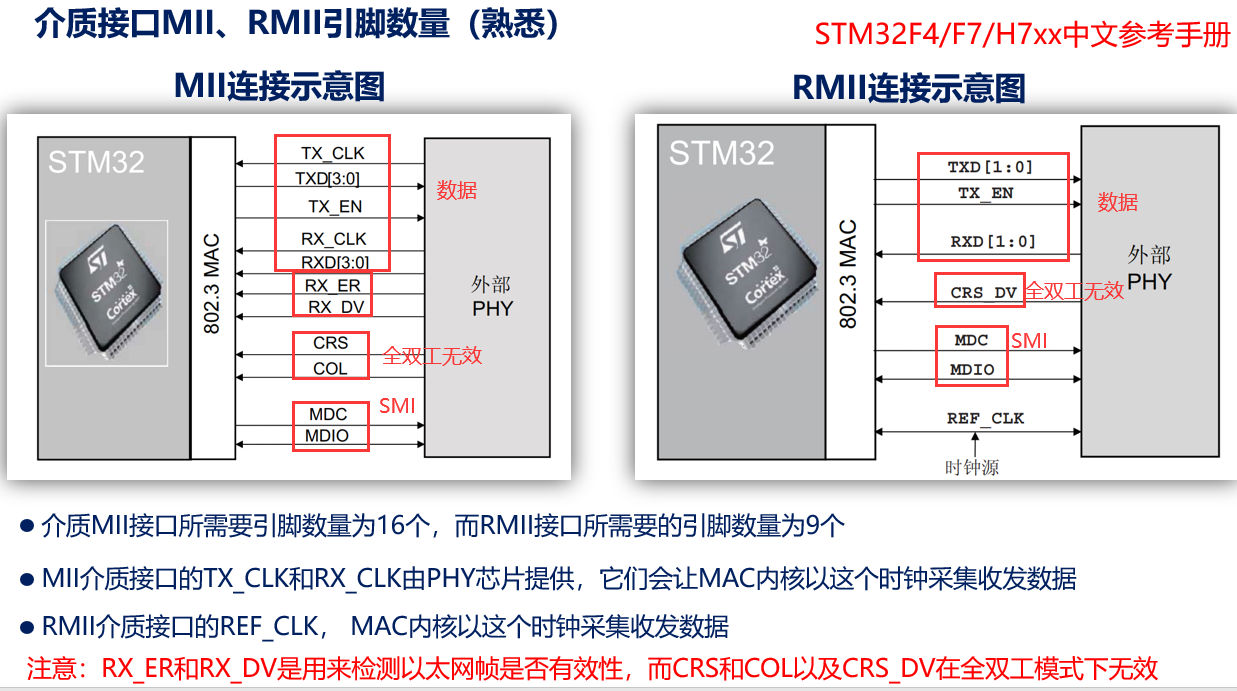

MII/RMII接口

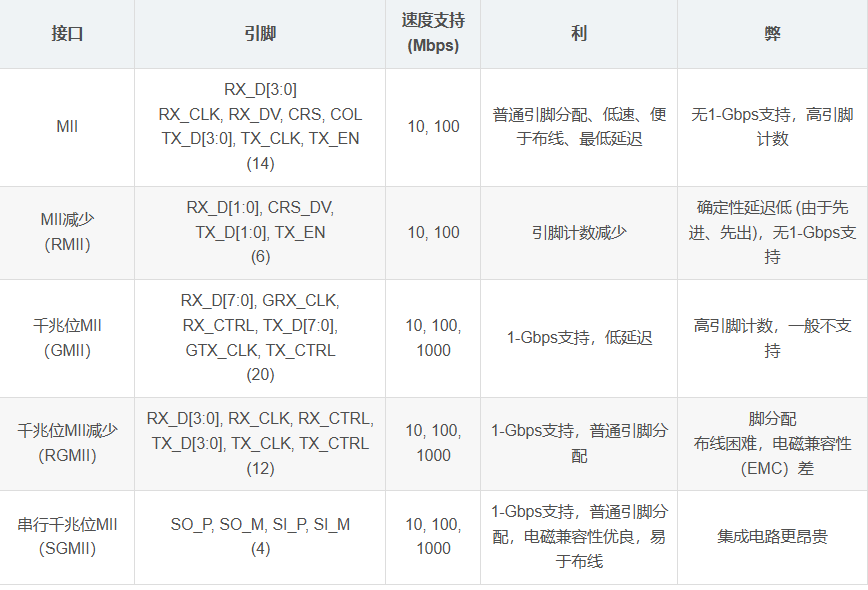

MII(Media Independent Interface)即媒体独立接口,MII接口是MAC与PHY连接的标准接口。它是IEEE-802.3定义的以太网行业标准。MII接口提供了MAC与PHY之间、PHY与STA(Station Management)之间的互联技术。媒体独立表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作.它包括一个数据接口,以及一个MAC和PHY之间的管理接口。MII接口有MII、RMII、SMII、SSMII、SSSMII、GMII、SGMII、RGMII等。这里简要介绍其中的MII和RGMII。

MII接口主要包括以下三个部分:

- 从MAC层到PHY层的发送数据接口

- 从PHY层到MAC层的接收数据接口

- 从MAC层和PHY层之间寄存器控制和信息获取的MDIO接口

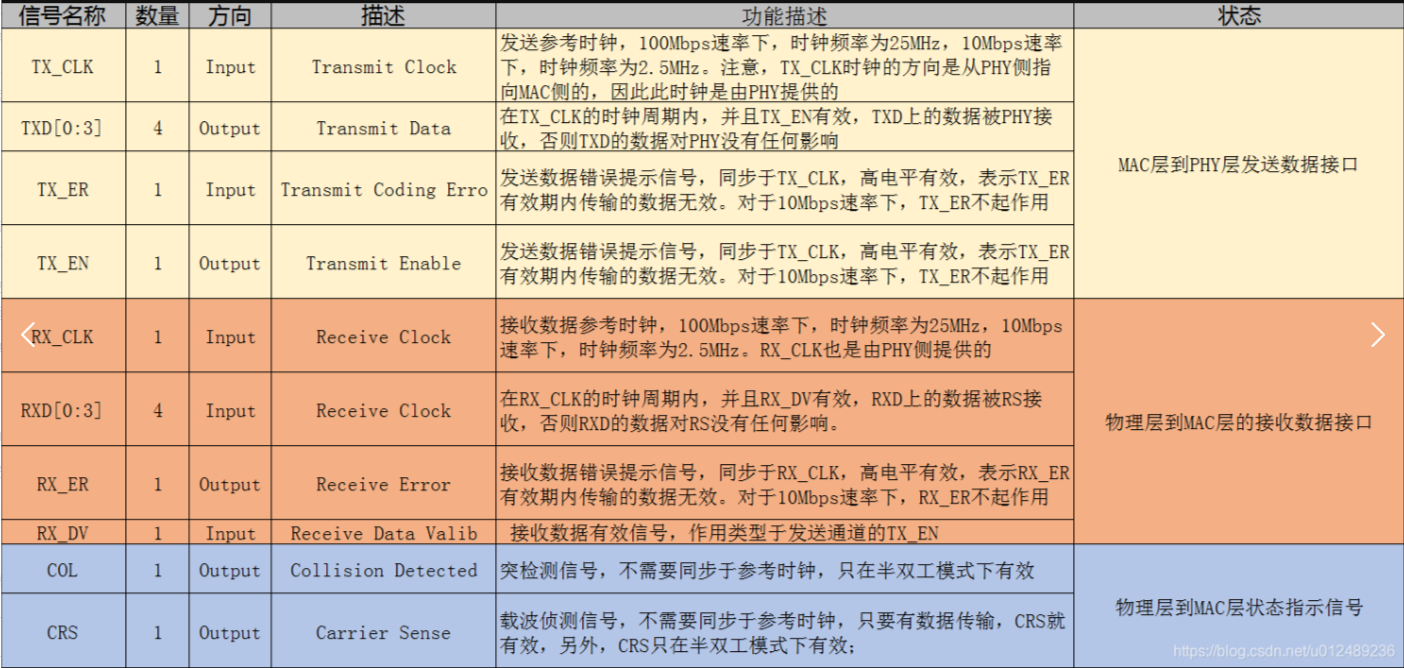

首先来看看MII的MAC层定义接口

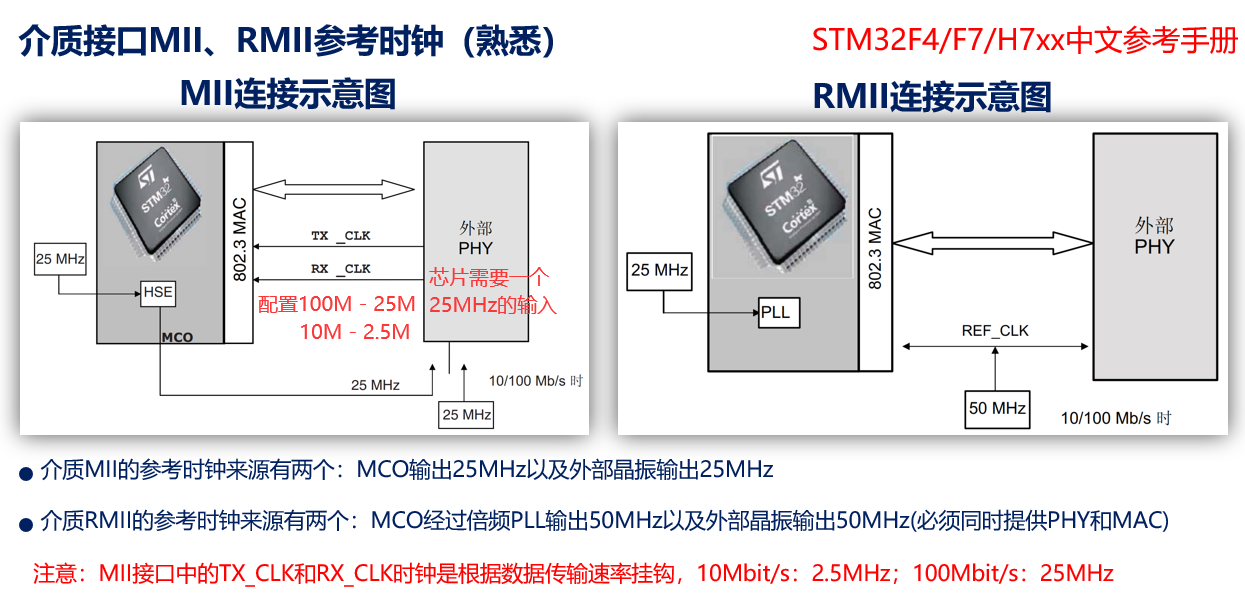

MII 数据接口总共需要 16 个信号,包括 TX_ER,TXD[3:0],TX_EN,TX_CLK,COL,RXD[3:0],RX_ER,RX_CLK,CRS,RX_DV 等。MII的时钟为25MHz,传输速率为10/100Mbps。所以MII的特性如下:

- 支持10Mb/s和100Mb/s的数据速率

- 100M工作模式下,参考时钟是25MHz;10M工作模式下,信号参考时钟是2.5MHz

- 支持全双工、半双工两种工作模式

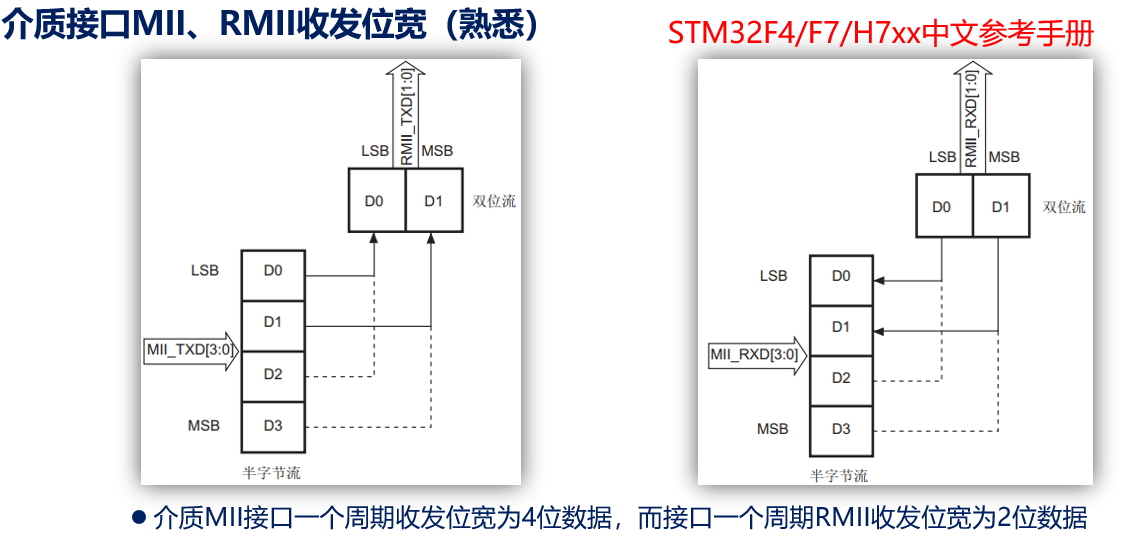

- 发送和接收数据时采用,4bit方式

RMII的用途: RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线(2数据位),所以它一般要求是50MHz的总线时钟。RMII一般用在多端口的交换机,所有的数据端口公用一个时钟用于所有端口的收发,这里就节省了不少的端口数目.RMII的一个端口要求7个数据线,比MII少了一倍,所以交换机能够接入多一倍数据的端口.和MII一样,RMII支持10Mbps和100Mbps的总线接口速度.

后来为了支持千兆网口,也就开始有了千兆网的MII接口,也就是GMII接口。现在比较常用的是RGMII,减小了MAC和PHY之间的引脚数量。数据信号和控制信号混合在一起,并且在工作时钟的上升沿和下降沿同时采样,其对应关系图如下:

- 10M带宽对应的是2.5MHz,因为4bit2.5M=10Mbps

- 100M带宽对应的是25MHz,因为4bit25M=100Mbps

- 1000M带宽对应的是125MHz,因为250MHz频率太高,所以采用双边沿采样技术(会带来设计复杂度)。4bit125M2=1000Mbps

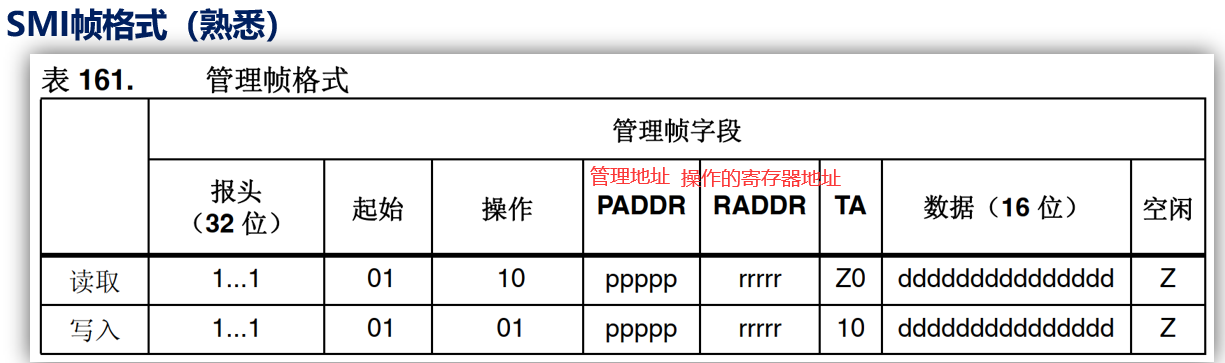

SMI管理系统

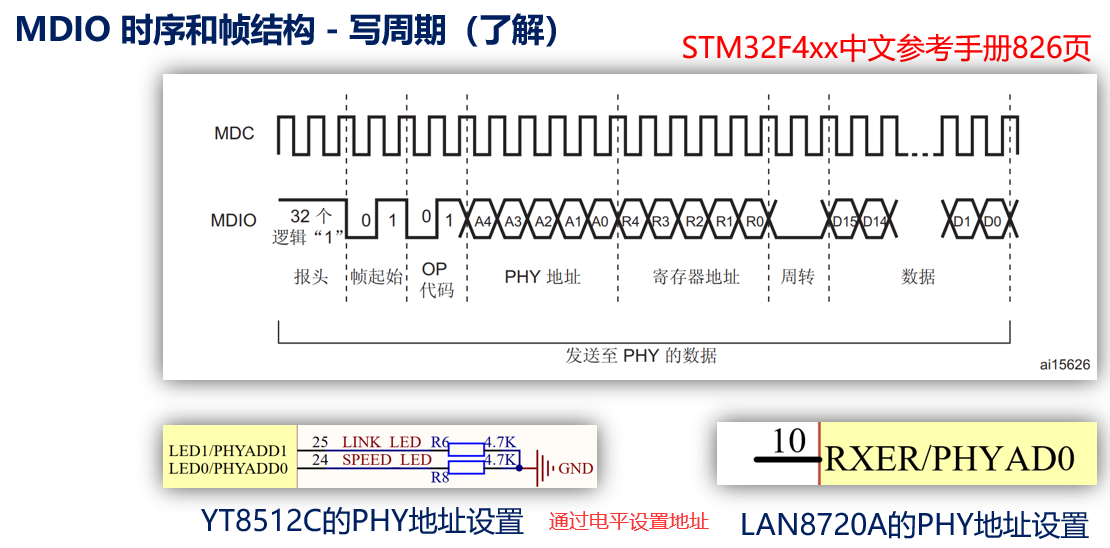

管理通道是下面的两条线, 实际的作用是管理多个PHY设备, 最多可以有32个PHY芯片

- MDC: 时钟引脚, 最大2.5MHz

- MDIC: 数据输出/输入比特流

PHY芯片

是一个模数混合的芯片, 这一个芯片可以接受光电信号, 经过解调和AD转换以后通过MII和RMII信号传递给MAC内核

它们都是低功耗的10/100M以太网PHY层芯片,支持MII以及RMII接口与以太网MAC层通信。支持Auto MDIX自动翻转功能,无需更换网线即可将连接更改为直连或交叉连接。

Auto MDIX(Automatic Medium-Dependent Interface Crossover)是一种以太网技术,它允许设备自动检测和纠正线中的连接错误。这样可以使得使用直通线缆(般用于连接计算机和交换机)或交叉线缆一般用于连接交换机和路由器)来连接设备都能正常工作。

在网络设备上启用Auto MDIX后,它将自动识别所使用的网线类型,并根据需要内部调整以适应该类型的网线。因此,用户无需关心所使用的是直通线还是交叉。

地址: SMI站管理通过PHY的地址访问指定的PHY芯片, 简称标识, 一般使用芯片的引脚进行设置

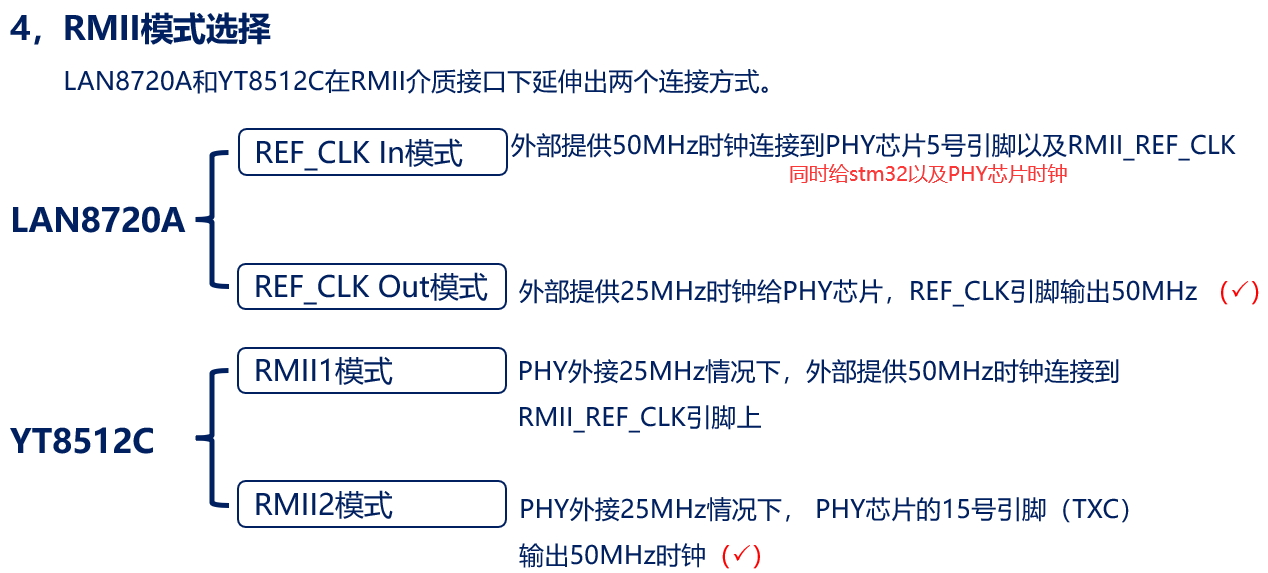

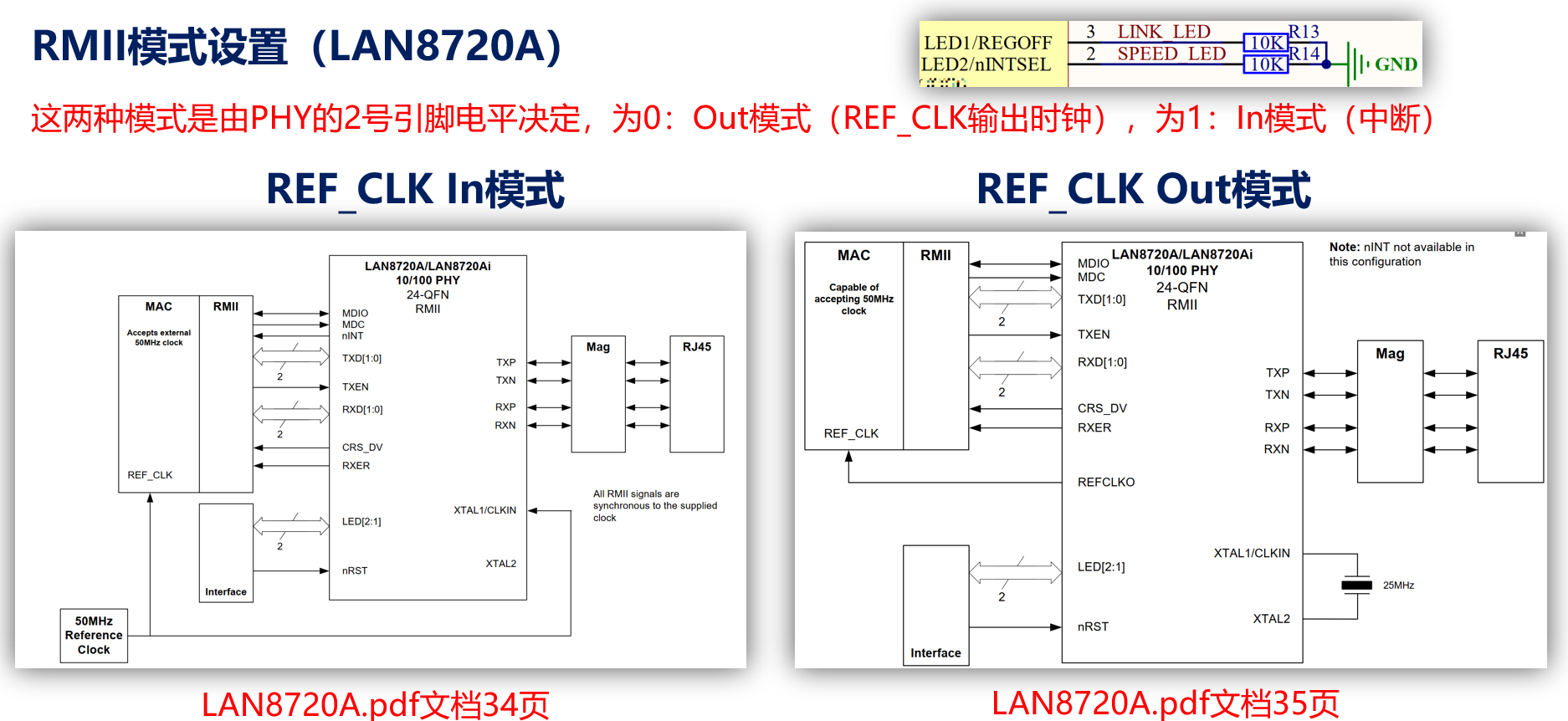

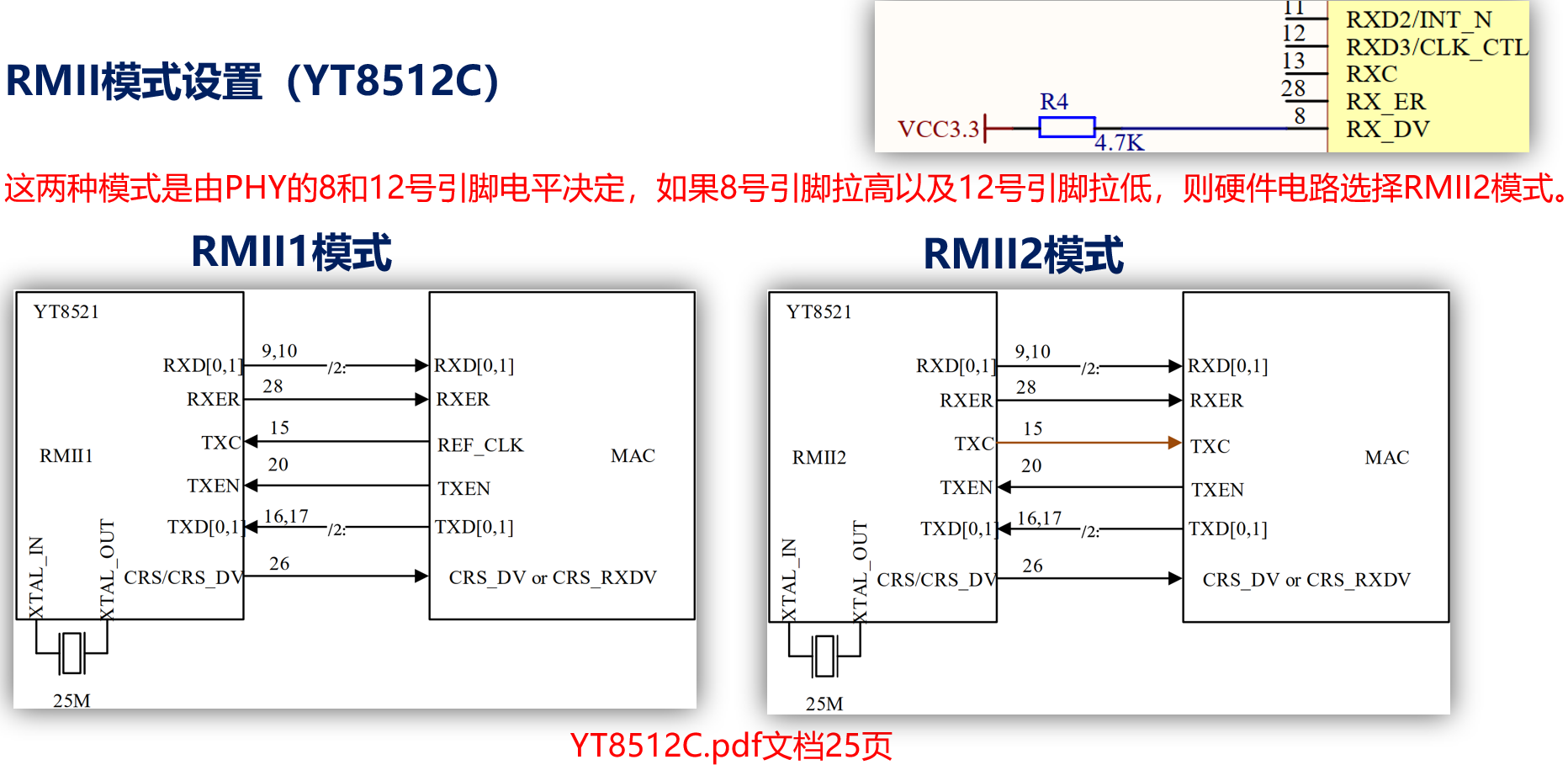

时钟模式

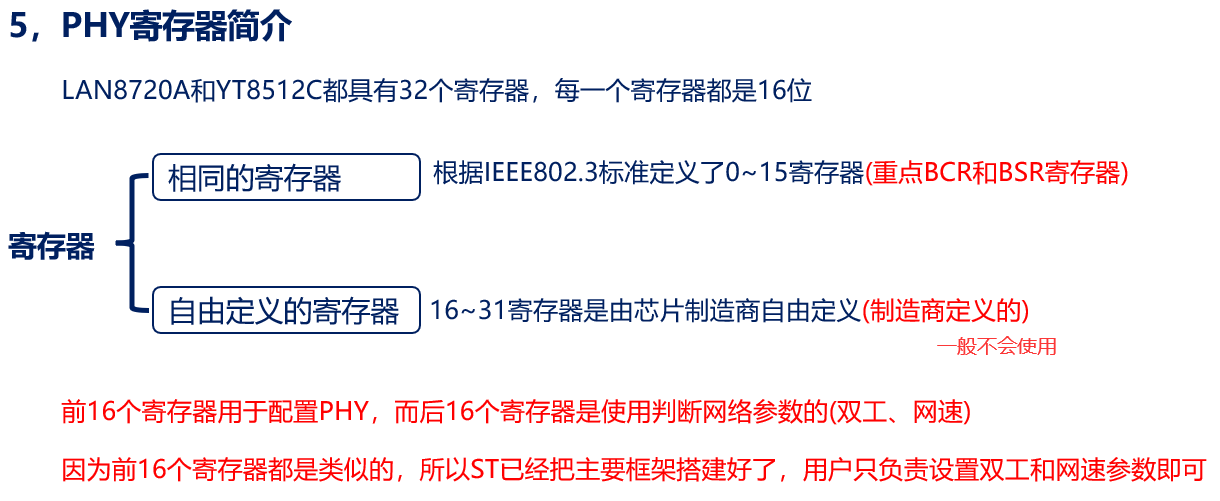

寄存器

可以通过BCR寄存器(0)设置速率以及, 13位为速度, 8位为全双工半双工

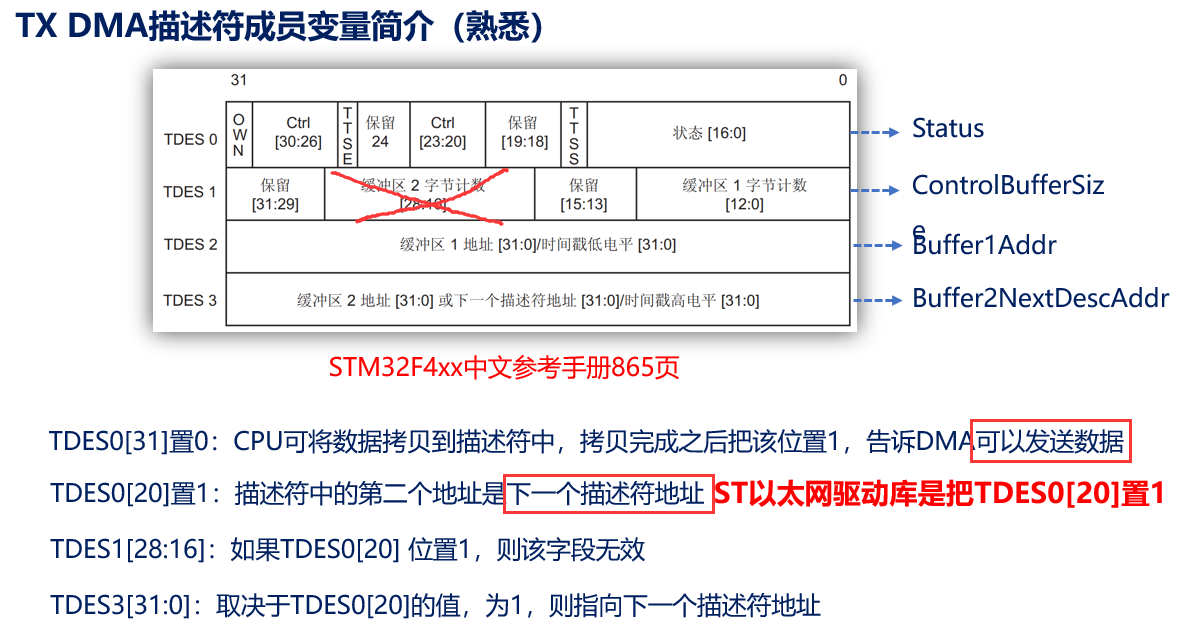

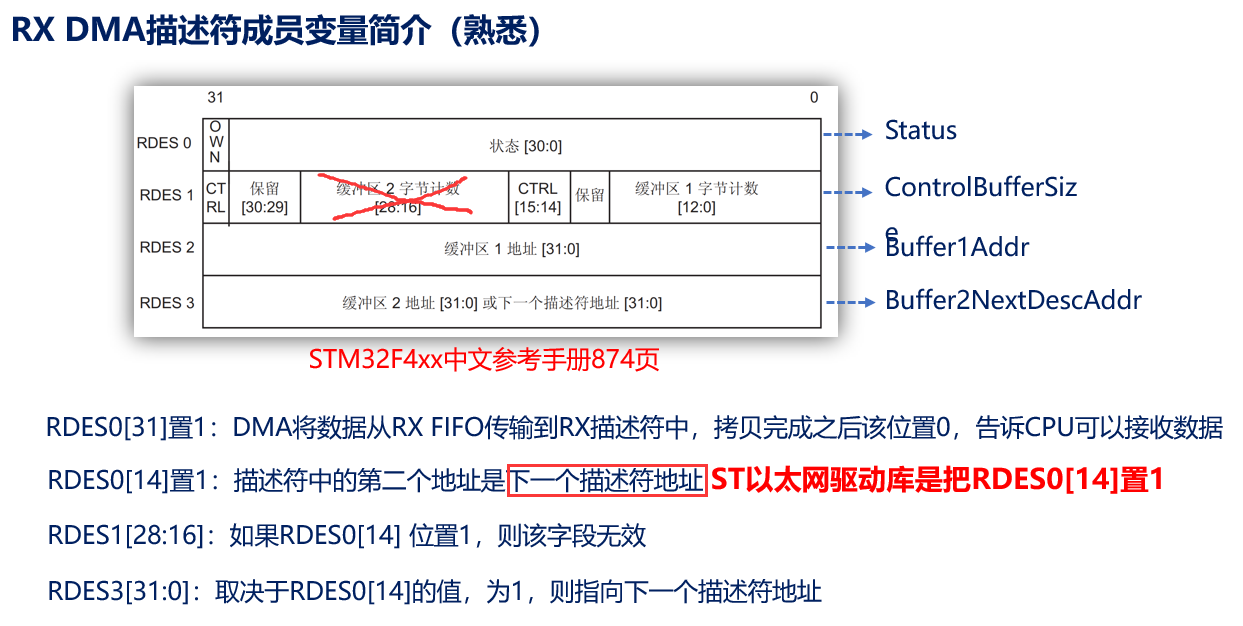

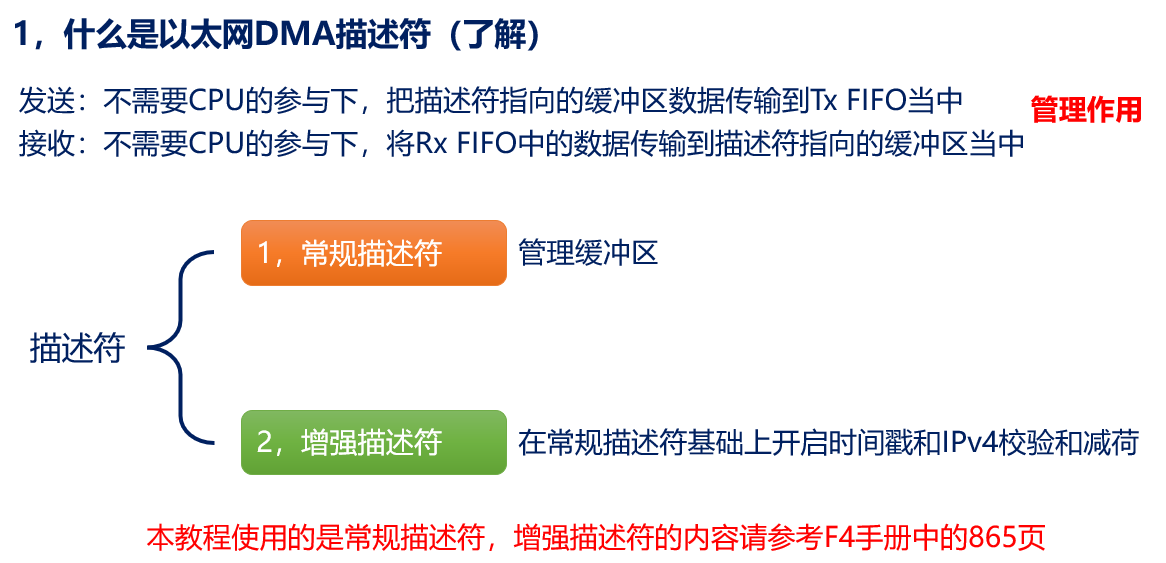

以太网DMA描述符

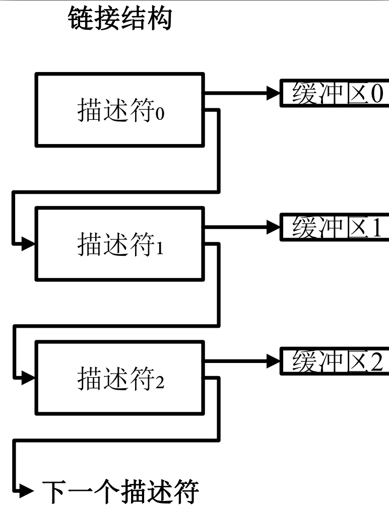

实际发送数据的时候需要使用以太网DMA, 在实际的工程里面它起到的作用是发送的时候把描述符指向的缓冲区数据传递到TxFIFO里面吗接收的时候吧RxFIFO里面的数据传递到指向的缓冲区里面

c

typedef struct

{

__IO uint32_t Status; /* 状态 */

uint32_t ControlBufferSize; /* 缓冲区1和2的大小 */

uint32_t Buffer1Addr; /* 缓冲区1的地址 */

uint32_t Buffer2NextDescAddr; /* 缓冲区2的地址/指向下一个描述符 */

/* 以下成员变量为增强描述符的 */

/* ……………………*/

}

ETH_DMADescTypeDef;

在实际实现的时候, 使用ETH_InitTypeDef里面的两个变量, RxDesc和TxDesc进行追踪