Appearance

FSMC(SRAM)

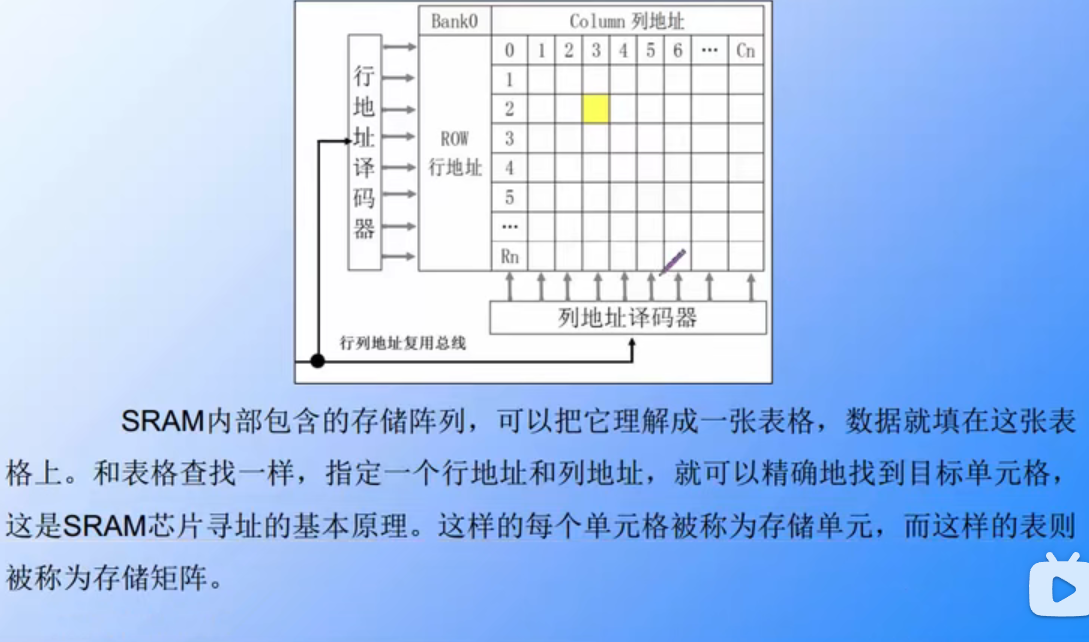

SRAM

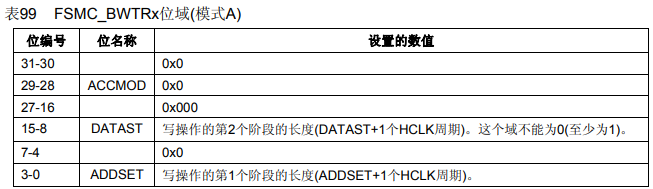

芯片里面有SRAM相当于内存条, 可以使用用来扩展

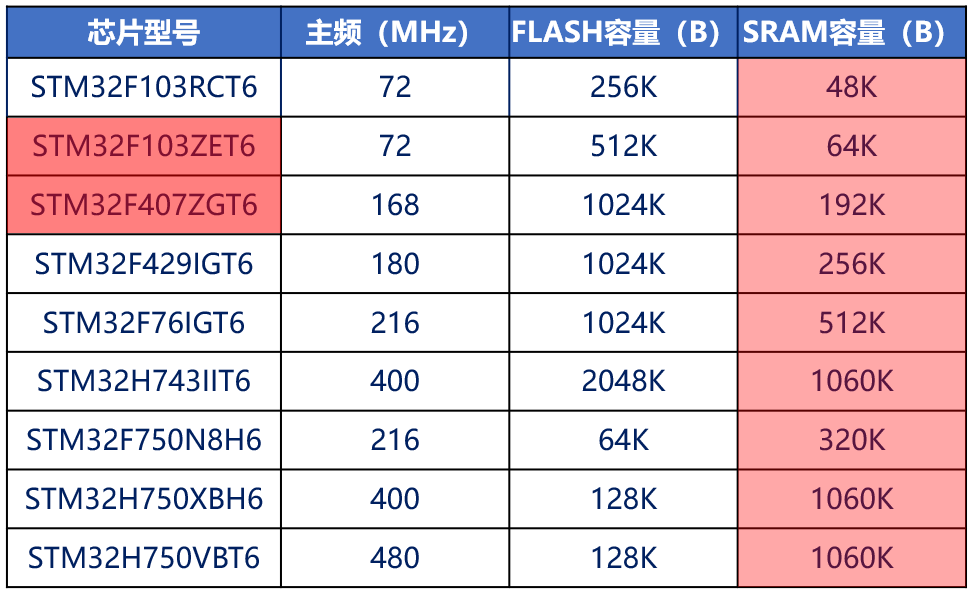

IS62WV51216ALL

①用来存储数据

②地址数据转换电路

③控制电路

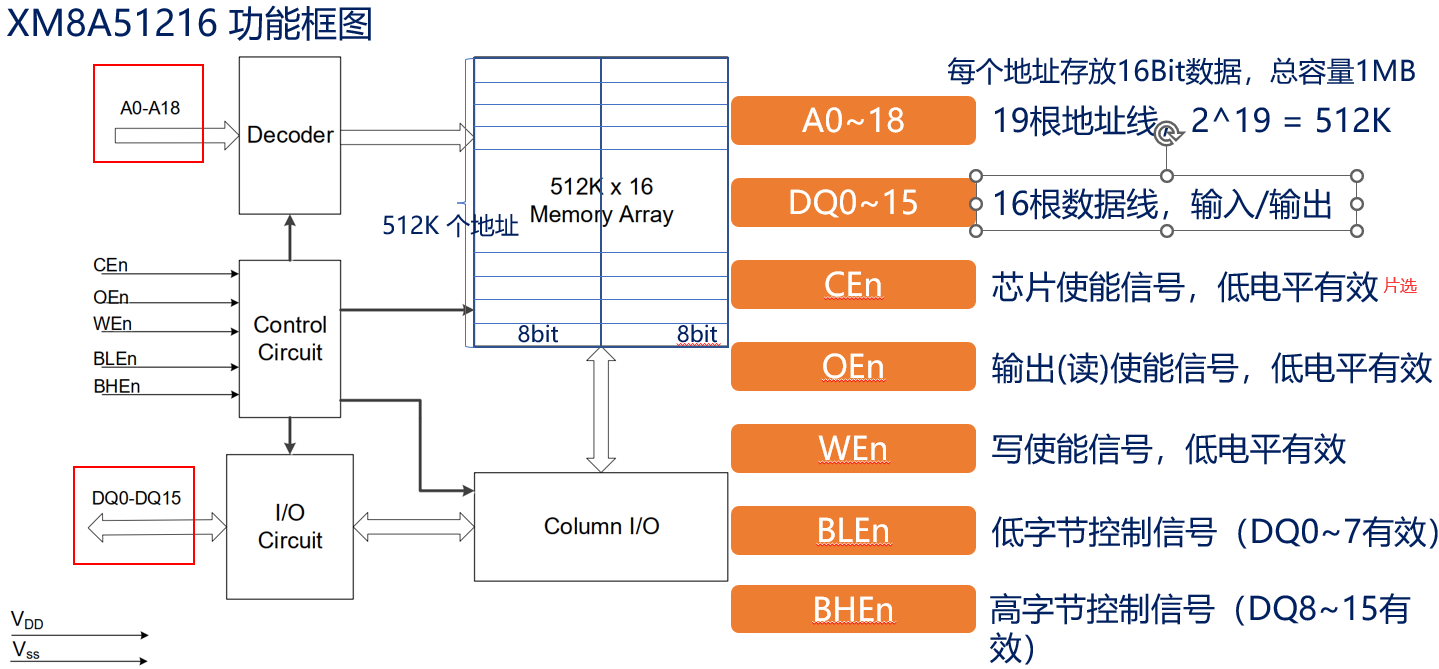

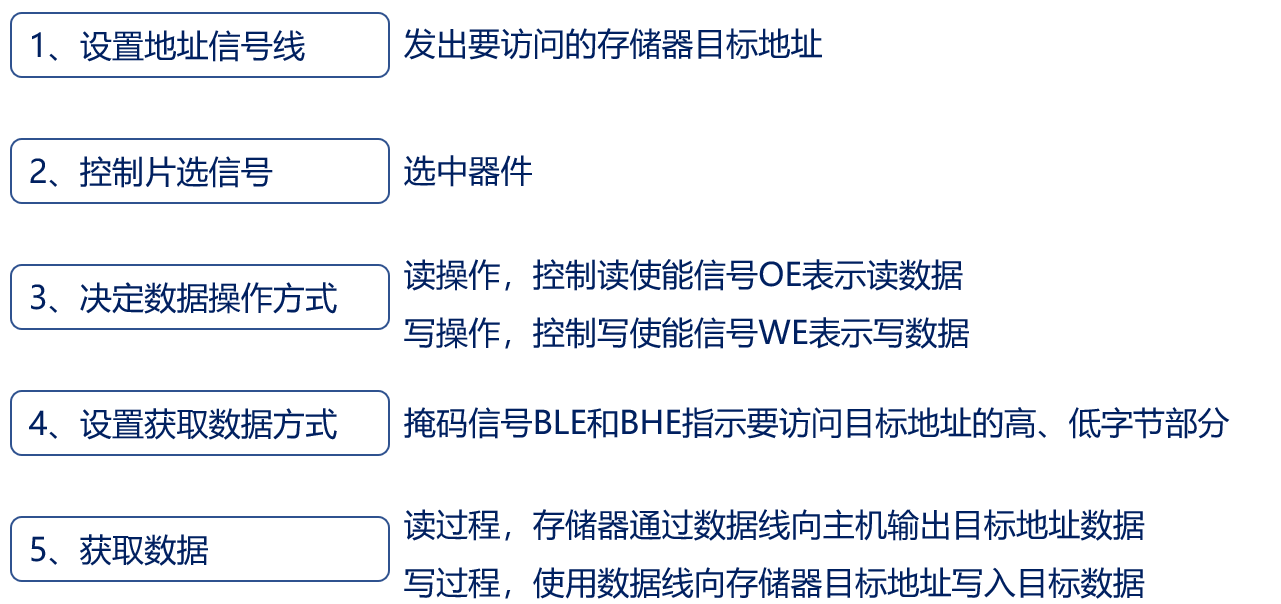

在寻址的时候每个地址有16位数字, 想要输出其中第一字节或者第二字节字节, 使用UB或者LB为低电平控制数据有效

OE: 读使能

CS: 片选

WE: 写使能

2^18^个数据位, 就是512K个数据位, 每个数据为是16位, 所以一共是1M字节

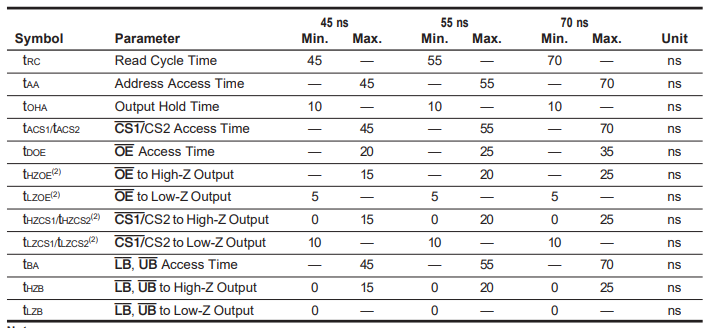

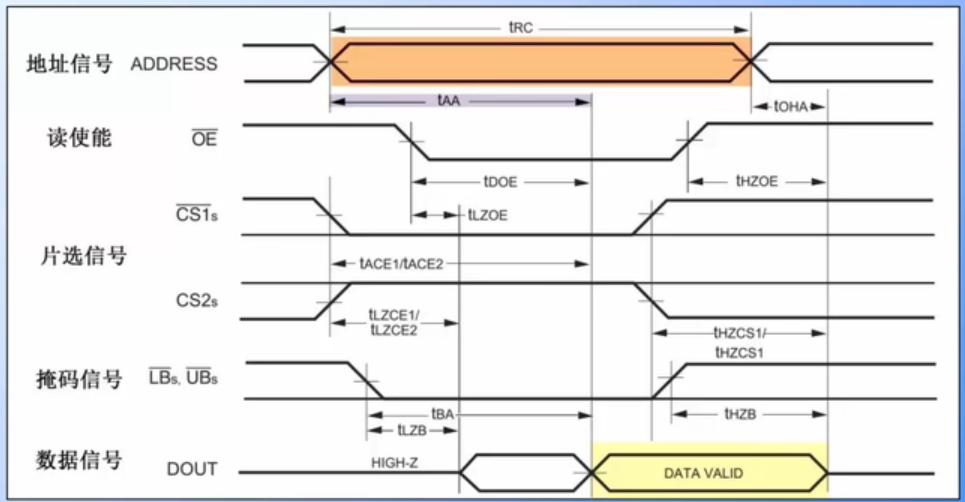

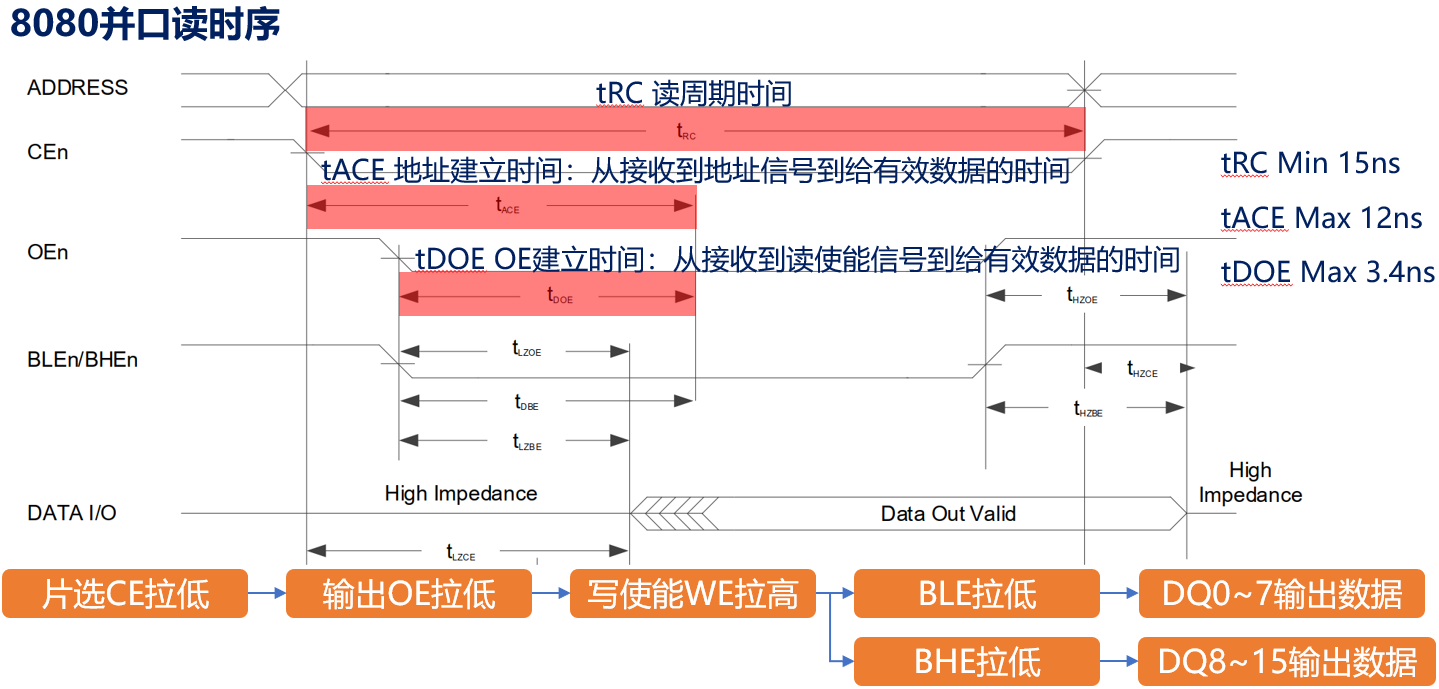

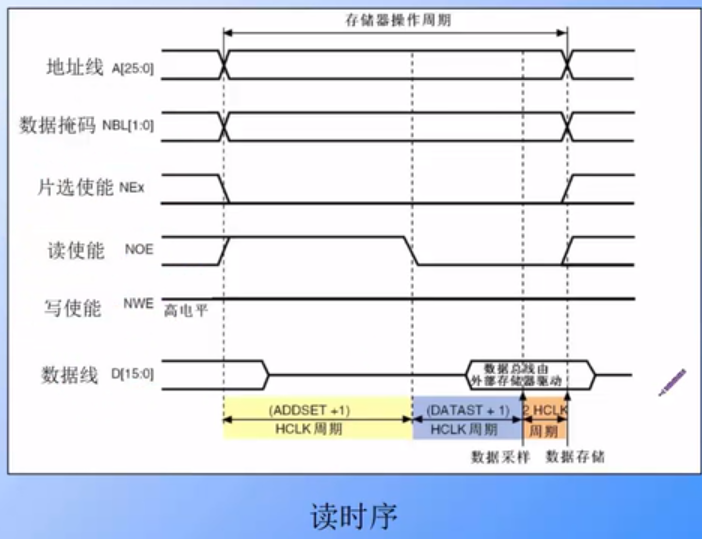

读

通过时间协调进行通讯

片选,同时输入地址, 控制掩码, 传入地址, 读使能, 一段时间后返还数据, 保持一段时间

没有时钟同步, 所以需要时间数据

主要是TRC, TAA, TDOE

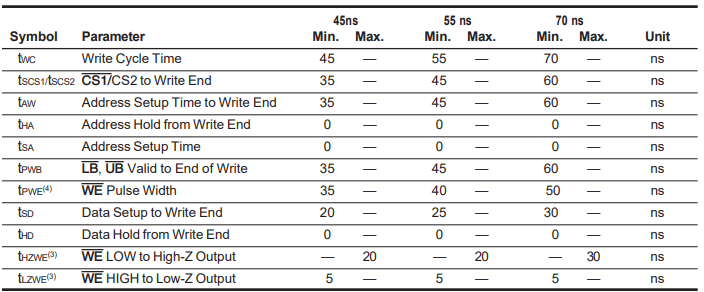

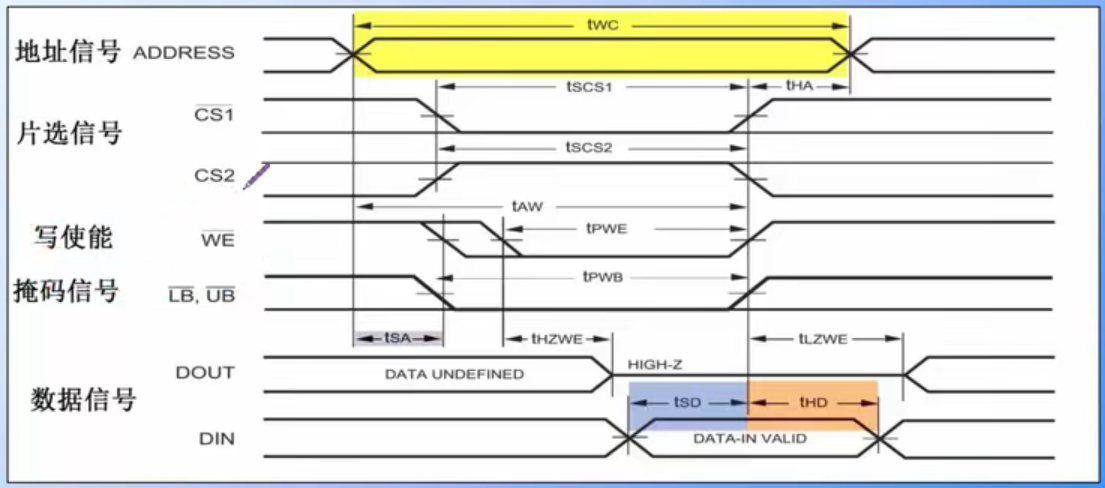

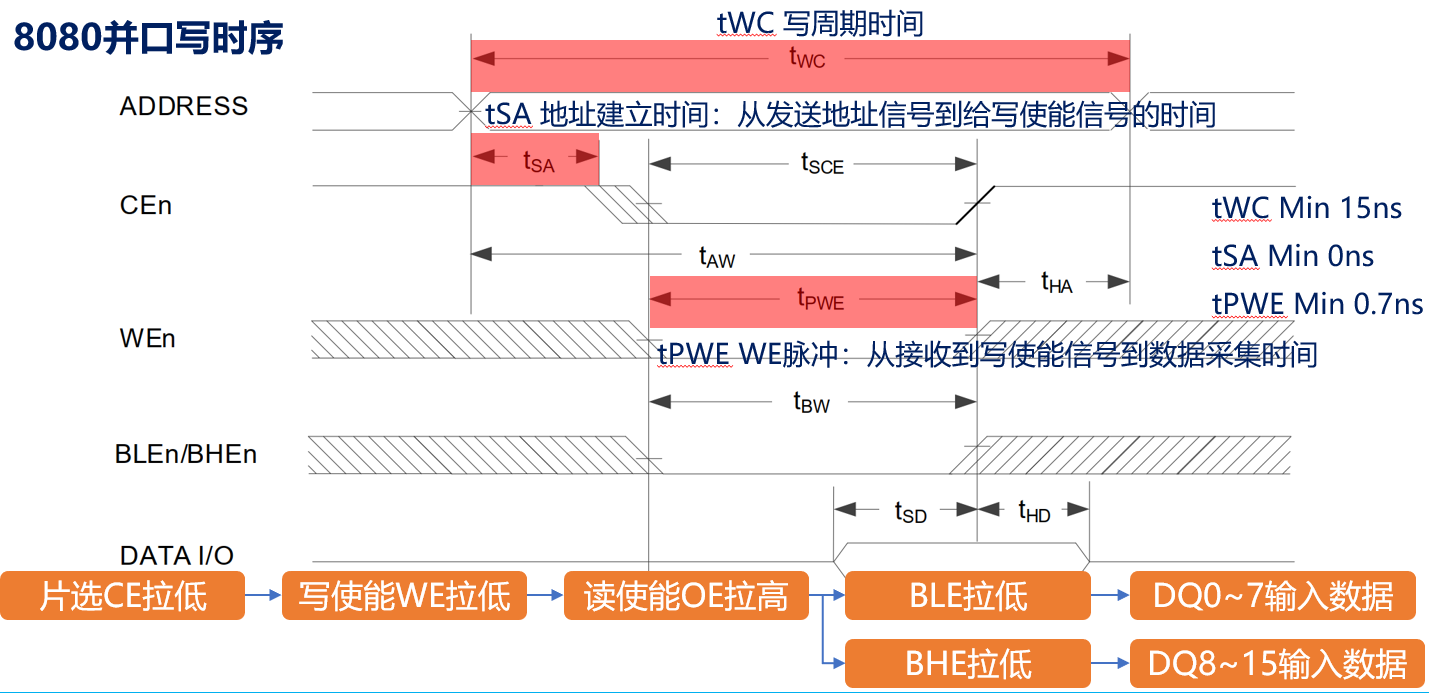

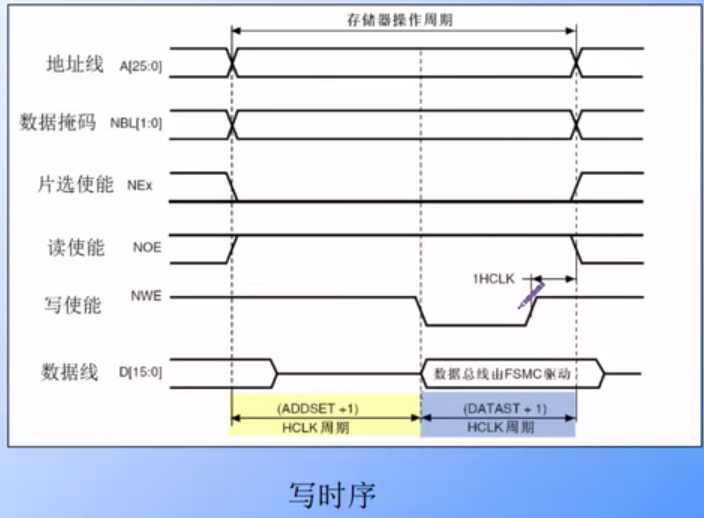

写

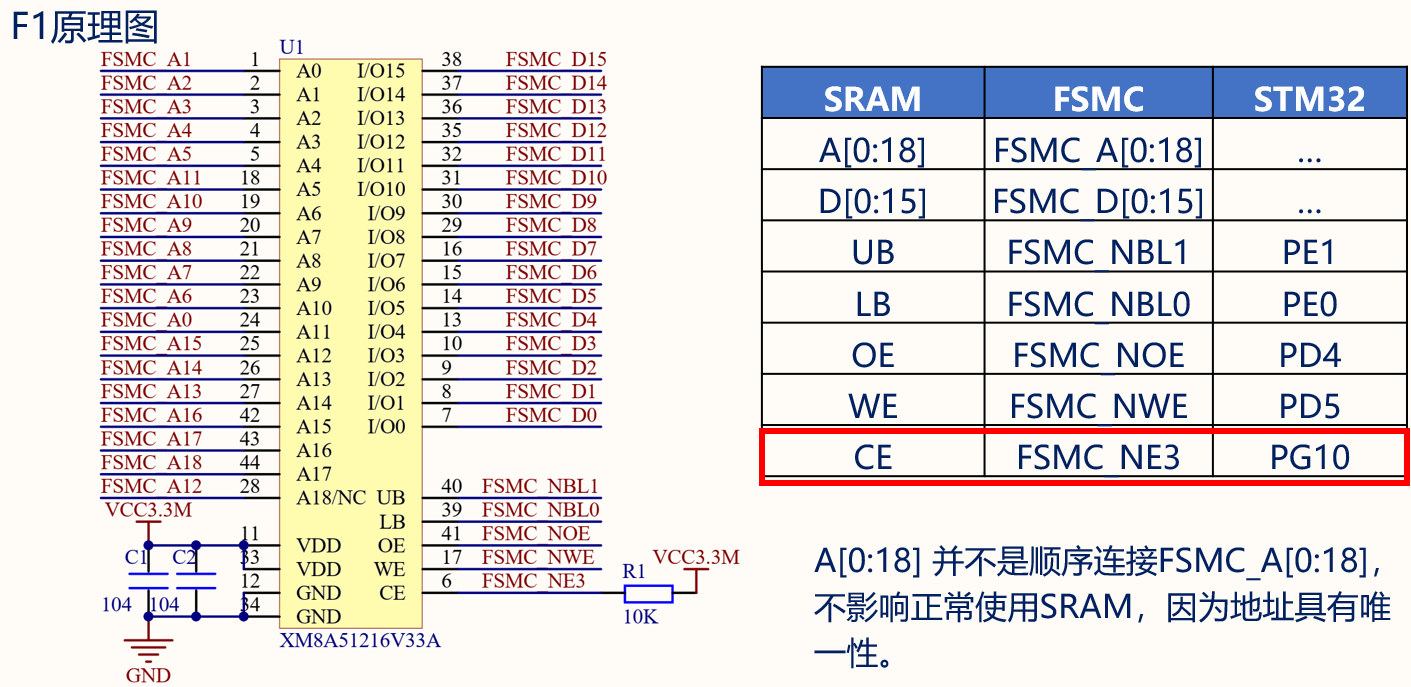

XM8A51216

最高访问速度是15ns, 功耗比较低, TTL电平兼容, 全静态操作, 不需要刷新电路以及时钟电路

三态输出, 支持高低字节

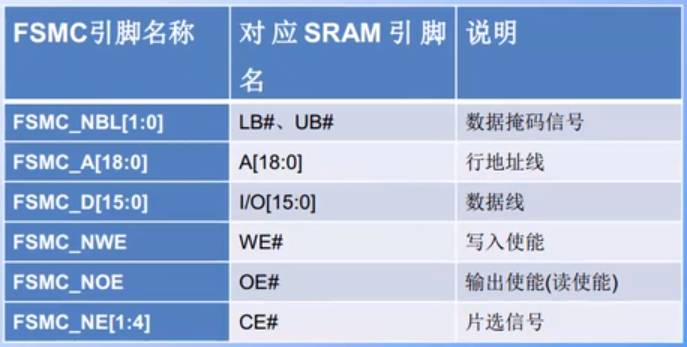

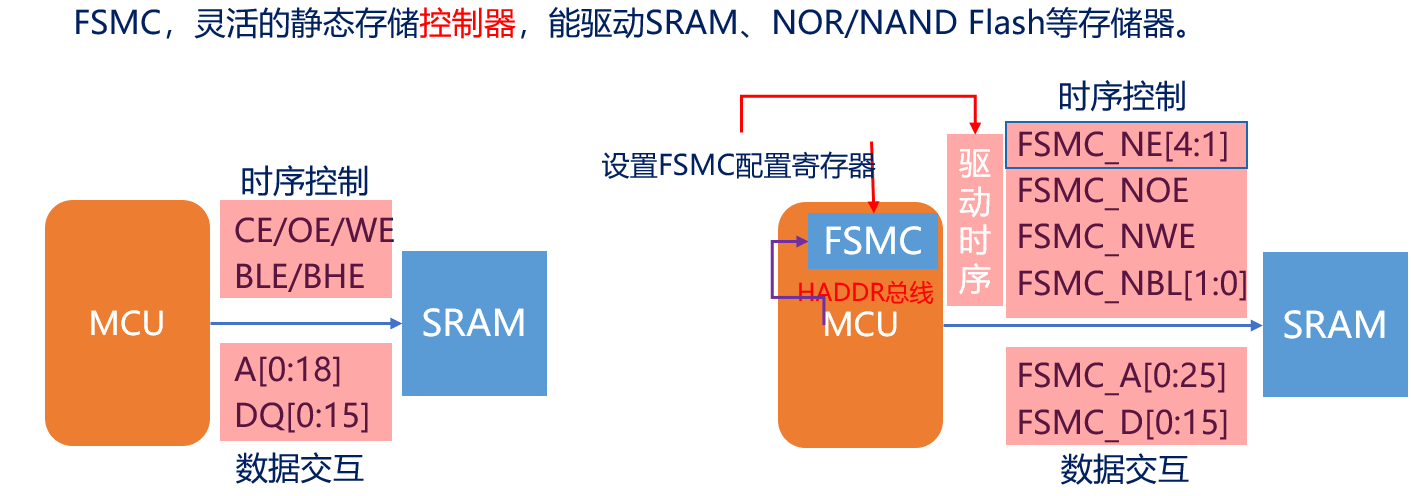

NE: 片选信号, NBL: 掩码信号, NOE, NWE: 选择读或者写

stm32的实现

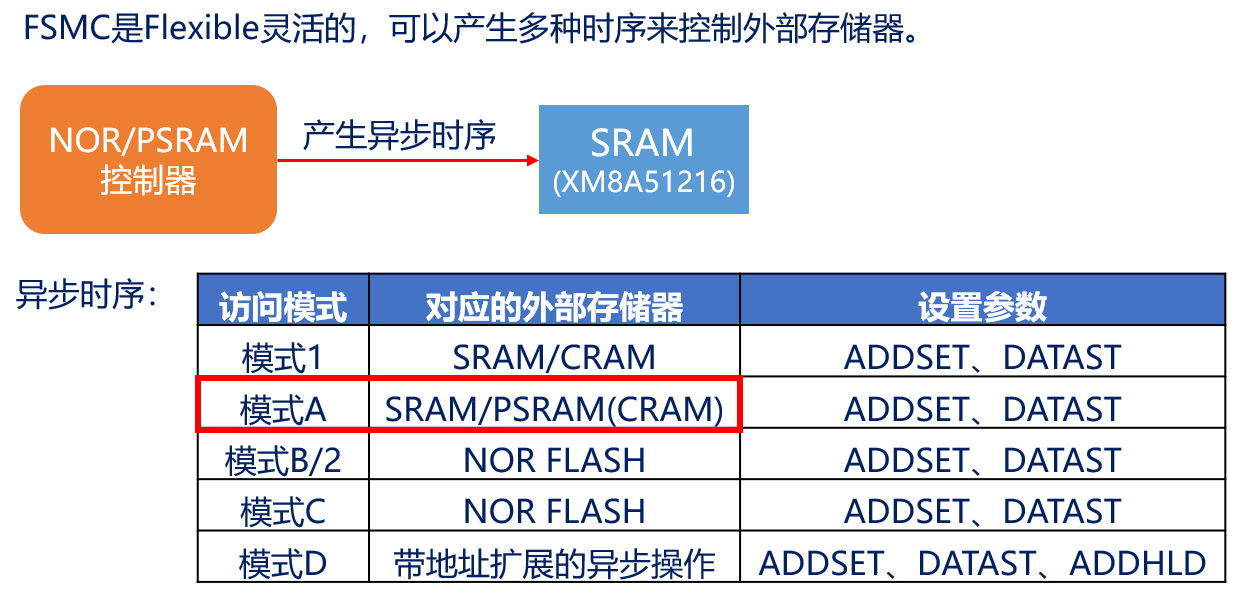

FSMC: 灵活的静态存储器

用来控制SRAM, ROM

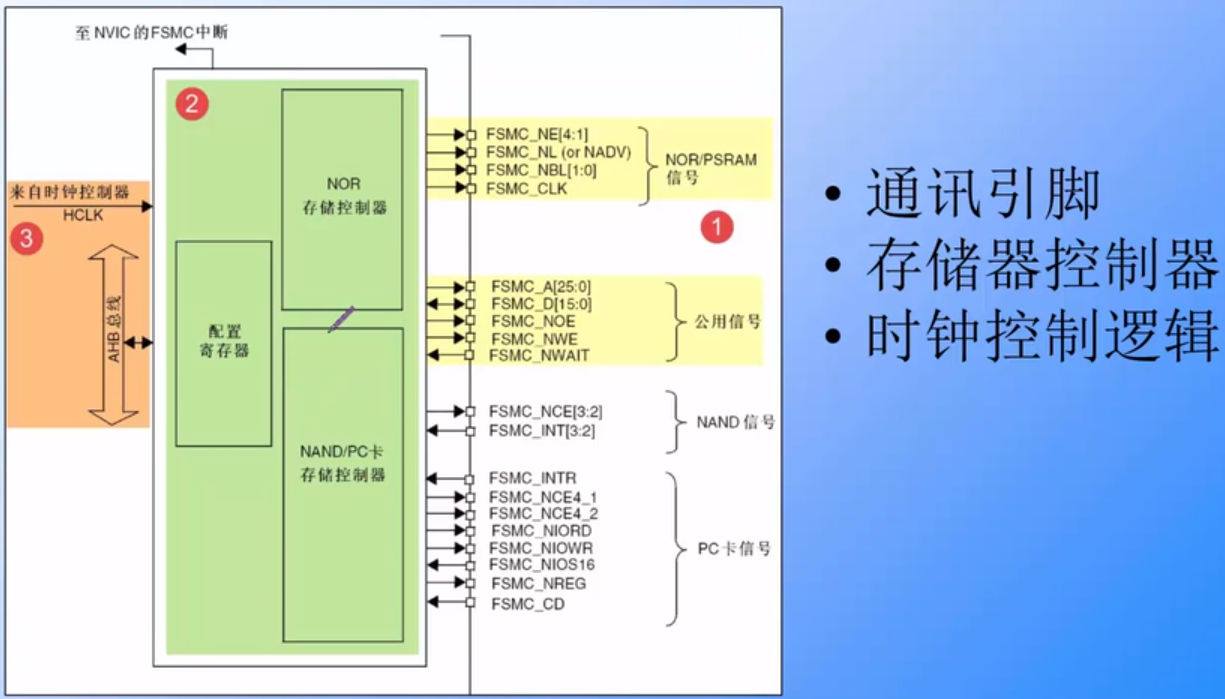

引脚

FSMC_NB: 控制数据的高位低位

FSMC_A: 地址线, 这里只使用了一部分

FSMC_D: 数据线

FSMC_NWE: 写入时能

FSMC_NOE: 输出使能

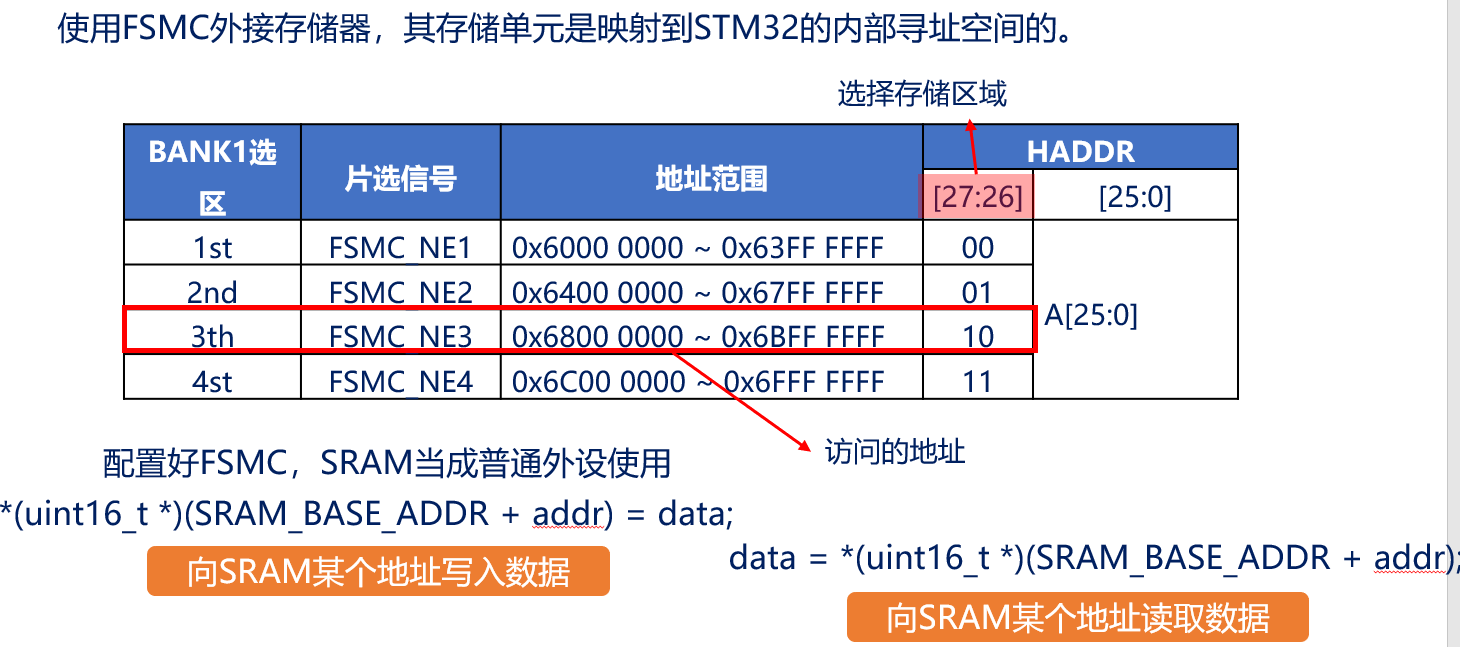

FSMSC_NE: 片选引脚, 控制不同的内部地址, stm32会把这片区域映射到自己的内存地址, 直接读写就可以了, 且可以挂载多个, 访问不同的空间的时候使能不同的引脚

存储器控制器

上面不同的引脚连接到FSMC内部对应的存储器中, NOR/PSRAM/SRAM设备使用相同的控制器, NAND/PC卡使用相同的控制器, 不同的控制器有不同的寄存器控制

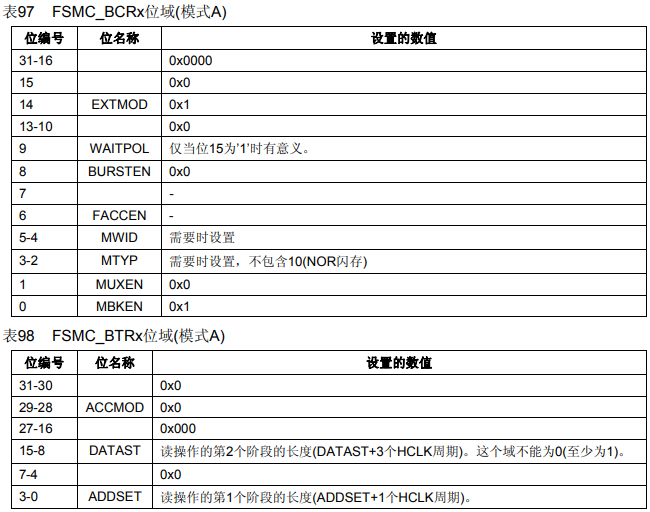

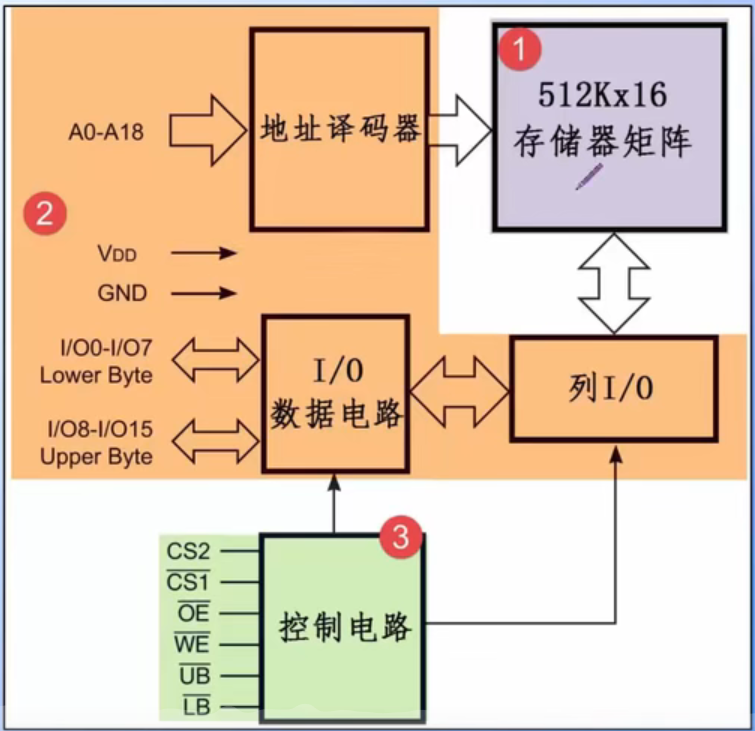

SRAM的寄存器有

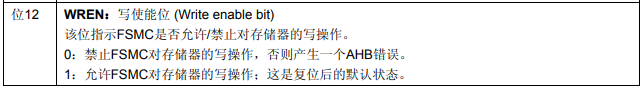

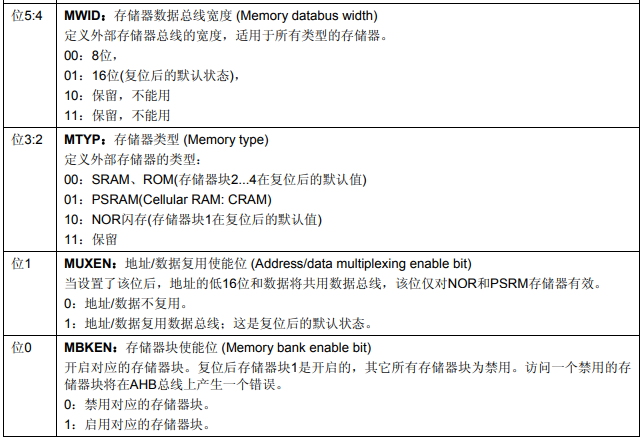

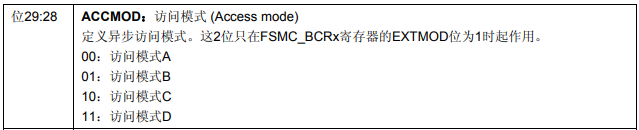

FSMC_BCRx: 控制寄存器, 控制存储器类型, 数据宽度, 信号有效极性

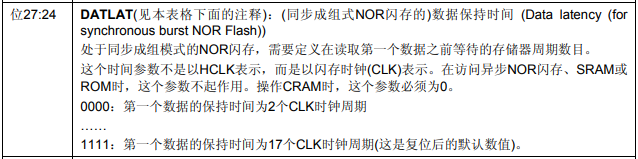

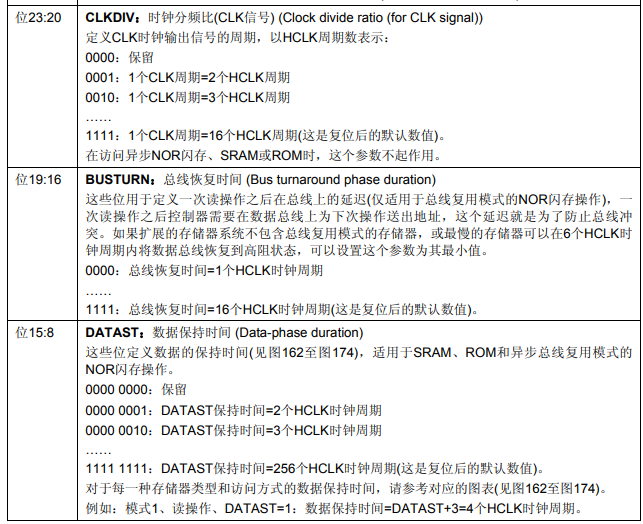

FSMC_BTRx: 片选时序寄存器, 控制延迟, 比如数据保持时间

不同的存储器使用不同的模式

① SRAM/CRAM

A: SRAM/PSRAM(CRAM)OE反转

②NOR闪存

C:NOR闪存OE反转

D: 带地址扩展异步操作

复用模式: 地址数据复用模式

FSMC_BWTRx: 写时序寄存器, 和上面基本一样, 主要用来扩展模式的时候读时序, 写时序使用不同的参数

时钟配置逻辑

直接连接在HCLK72MHz, 分频之后CLK引脚的频率会有变化, 这里没有使用, 为异步通讯

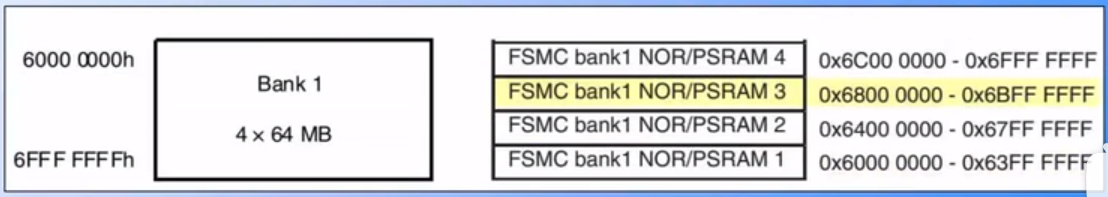

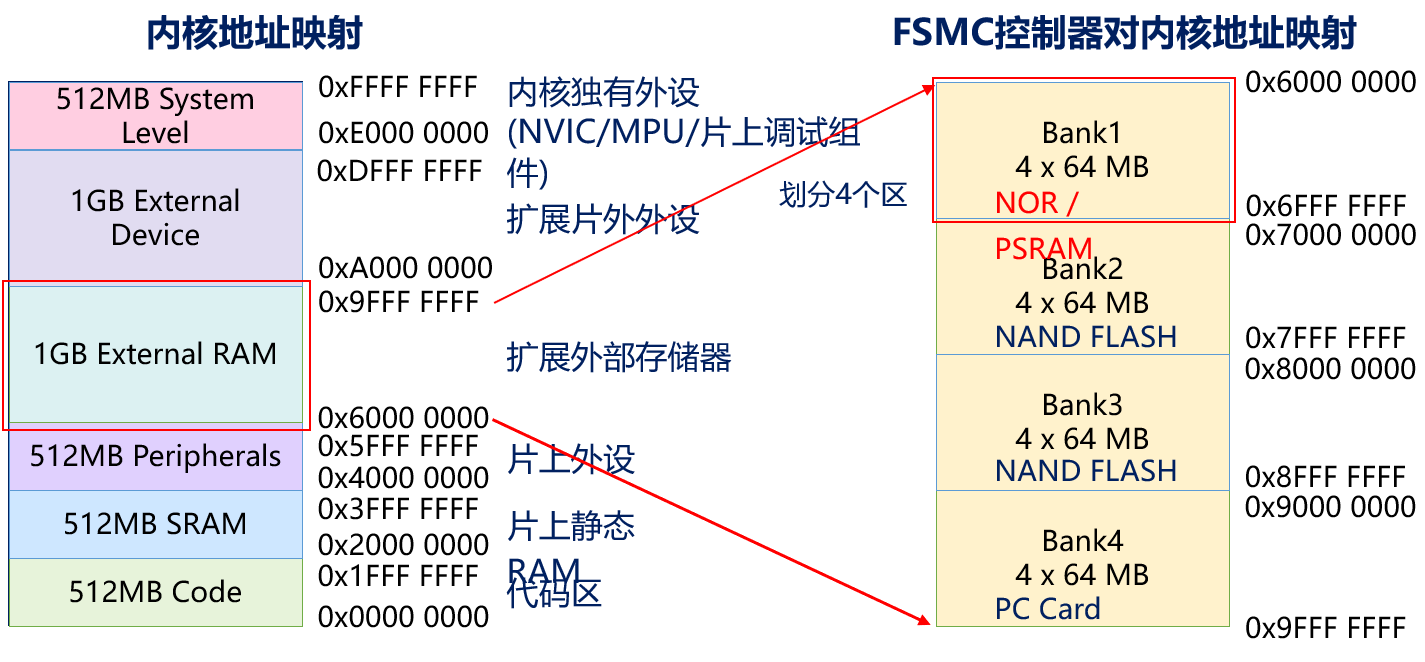

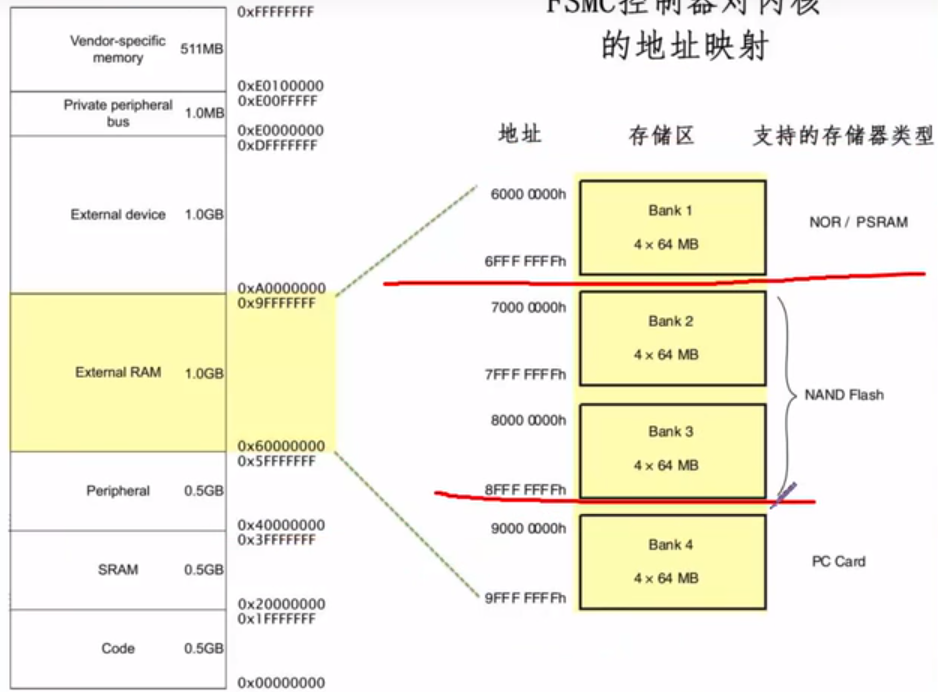

地址映射

直接映射到stm32自己的内存之中, 直接访问内存, stm32就会自动进行访问外部外设

stm预留了1G

每一个区域都有对应的存储器

为了连接不同的芯片, 每个信号线对应不同的引脚

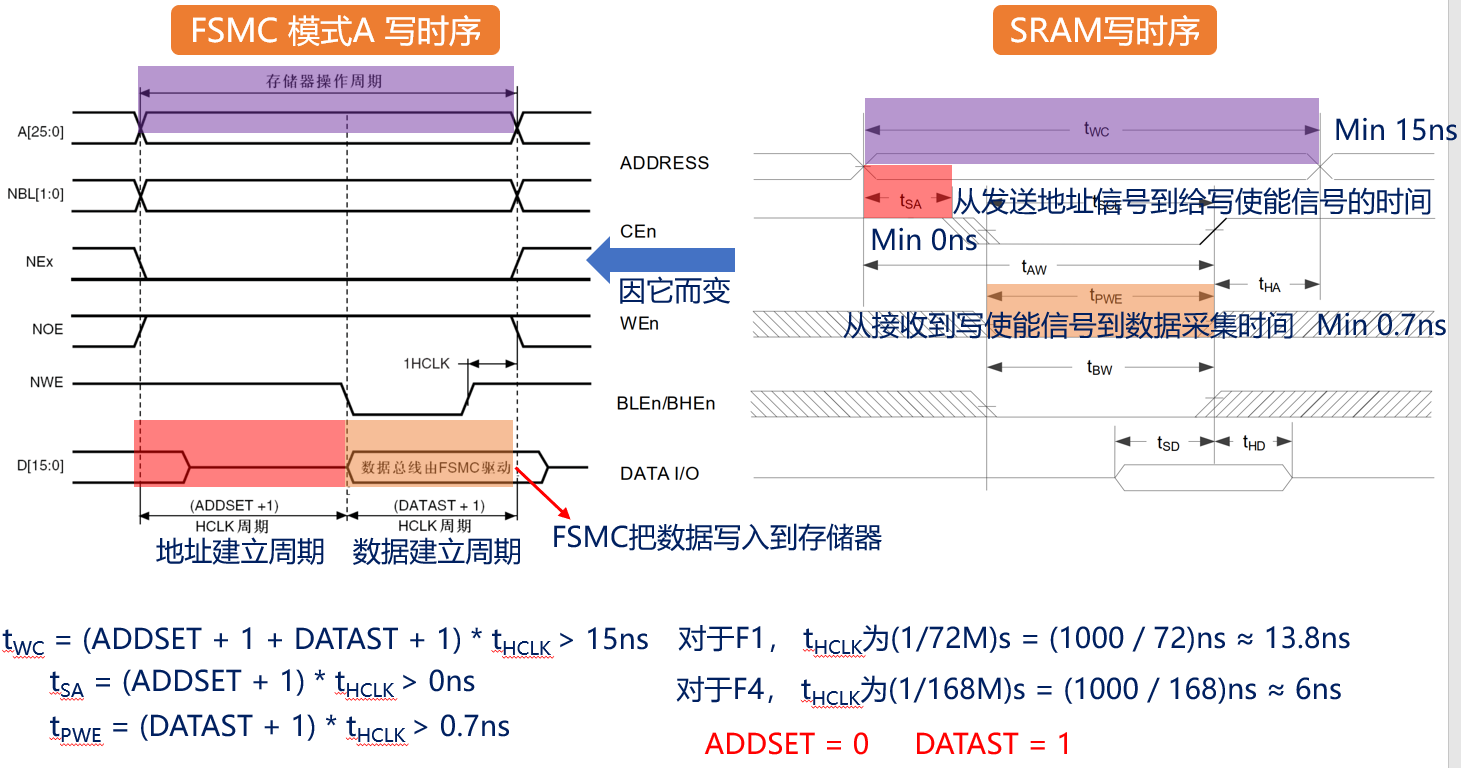

模式A

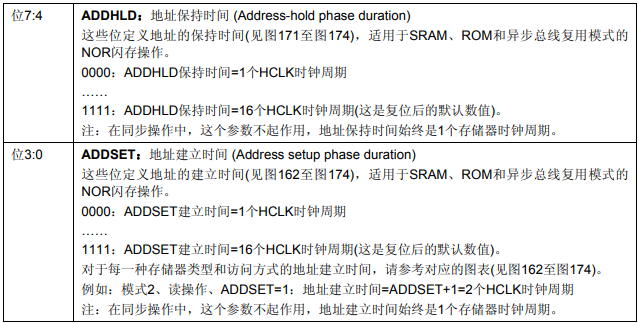

ADDSET小于TAA

DATAST+ADDSET时间大约就是tRC, 大于给出使能之后数据稳定的时间tDOE

所有的时间大于TRC=55ns

读使能到采样的时间大于TDOE, 最大是25ns

ADDSET没有限制

通过配置FSMC_BCR的EXTMOD位的时候可以控制读写时序是否一样

总时间小于tWC

采样是在写使能之后一段时间tPWE

写的总时间大于55ns: ADDSET+DARAST+2>=55ns

写使能到采样时间DATAST+1>40ns

地址配置之后可以立刻写使能

模式一和模式A的区别, 是否使用不同的时序

库函数

c

typedef struct

{

uint32_t FSMC_AddressSetupTime; /*!< Defines the number of HCLK cycles to configure

the duration of the address setup time.

This parameter can be a value between 0 and 0xF.

地址建立时间, 设置ADDSET, 设置之后会加一, 使能信号跳变的时刻*/

uint32_t FSMC_AddressHoldTime; /*!< Defines the number of HCLK cycles to configure

the duration of the address hold time.

This parameter can be a value between 0 and 0xF.

@note: It is not used with synchronous NOR Flash memories.

地址保持时间, ADDHALD模式, 是复用模式, 不关注*/

uint32_t FSMC_DataSetupTime; /*!< Defines the number of HCLK cycles to configure

the duration of the data setup time.

This parameter can be a value between 0 and 0xFF.

@note: It is used for SRAMs, ROMs and asynchronous multiplexed NOR Flash memories. 控制DATAST的时间, 设置0保留, 设置为1为两个时钟周期*/

uint32_t FSMC_BusTurnAroundDuration; /*!< Defines the number of HCLK cycles to configure

the duration of the bus turnaround.

This parameter can be a value between 0 and 0xF.

@note: It is only used for multiplexed NOR Flash memories.

总线转换周期,这个模式不使用*/

uint32_t FSMC_CLKDivision; /*!< Defines the period of CLK clock output signal, expressed in number of HCLK cycles.

This parameter can be a value between 1 and 0xF.

@note: This parameter is not used for asynchronous NOR Flash, SRAM or ROM accesses. 时钟分频因子, 输出时钟的时候使用,这里没有使用*/

uint32_t FSMC_DataLatency; /*!< Defines the number of memory clock cycles to issue

to the memory before getting the first data.

The value of this parameter depends on the memory type as shown below:

- It must be set to 0 in case of a CRAM

- It is don't care in asynchronous NOR, SRAM or ROM accesses

- It may assume a value between 0 and 0xF in NOR Flash memories

with synchronous burst mode enable 数据的保持时间, 这里也没有使用*/

uint32_t FSMC_AccessMode; /*!< Specifies the asynchronous access mode.

This parameter can be a value of @ref FSMC_Access_Mode 选择访问模式

这里使用模式A*/

}FSMC_NORSRAMTimingInitTypeDef;配置时钟的结构体

c

typedef struct

{

uint32_t FSMC_Bank; /*!< Specifies the NOR/SRAM memory bank that will be used.

This parameter can be a value of @ref FSMC_NORSRAM_Bank

实际上控制的存储区, 实际选择是不同的寄存器组##使用##*/

uint32_t FSMC_DataAddressMux; /*!< Specifies whether the address and data values are

multiplexed on the databus or not.

This parameter can be a value of @ref FSMC_Data_Address_Bus_Multiplexing

地址线数据线是否复用*/

uint32_t FSMC_MemoryType; /*!< Specifies the type of external memory attached to

the corresponding memory bank.

This parameter can be a value of @ref FSMC_Memory_Type

控制的是存储器的类型##使用##*/

uint32_t FSMC_MemoryDataWidth; /*!< Specifies the external memory device width.

This parameter can be a value of @ref FSMC_Data_Width

配置数据位的大小##使用##*/

uint32_t FSMC_BurstAccessMode; /*!< Enables or disables the burst access mode for Flash memory,

valid only with synchronous burst Flash memories.

This parameter can be a value of @ref FSMC_Burst_Access_Mode

配置是否使用突发模式, 给出起始地址,输入多个数据,地址会自动加一*/

uint32_t FSMC_AsynchronousWait; /*!< Enables or disables wait signal during asynchronous transfers,

valid only with asynchronous Flash memories.

This parameter can be a value of @ref FSMC_AsynchronousWait

是否使能同步传输的时候的等待信号*/

uint32_t FSMC_WaitSignalPolarity; /*!< Specifies the wait signal polarity, valid only when accessing

the Flash memory in burst mode.

This parameter can be a value of @ref FSMC_Wait_Signal_Polarity

设置等待信号的极性*/

uint32_t FSMC_WrapMode; /*!< Enables or disables the Wrapped burst access mode for Flash

memory, valid only when accessing Flash memories in burst mode.

This parameter can be a value of @ref FSMC_Wrap_Mode

设置是否支持对齐的突发模式*/

uint32_t FSMC_WaitSignalActive; /*!< Specifies if the wait signal is asserted by the memory one

clock cycle before the wait state or during the wait state,

valid only when accessing memories in burst mode.

This parameter can be a value of @ref FSMC_Wait_Timing

设置的那个带信号在等待前还是等待期间有效*/

uint32_t FSMC_WriteOperation; /*!< Enables or disables the write operation in the selected bank by the FSMC.

This parameter can be a value of @ref FSMC_Write_Operation

是否写使能##使用##*/

uint32_t FSMC_WaitSignal; /*!< Enables or disables the wait-state insertion via wait

signal, valid for Flash memory access in burst mode.

This parameter can be a value of @ref FSMC_Wait_Signal

是否能使能等待状态插入*/

uint32_t FSMC_ExtendedMode; /*!< Enables or disables the extended mode.

This parameter can be a value of @ref FSMC_Extended_Mode

是否使能扩展模式(使用两个时序)##使用##*/

uint32_t FSMC_WriteBurst; /*!< Enables or disables the write burst operation.

This parameter can be a value of @ref FSMC_Write_Burst

是否使能写的突发操作*/

FSMC_NORSRAMTimingInitTypeDef* FSMC_ReadWriteTimingStruct; /*!< Timing Parameters for write and read access if the ExtendedMode is not used, 读寄存器的时序, 或者在没有分开使用的时候使用的时序##使用##*/

FSMC_NORSRAMTimingInitTypeDef* FSMC_WriteTimingStruct; /*!< Timing Parameters for write access if the ExtendedMode is used 写寄存器的时序*/

}FSMC_NORSRAMInitTypeDef;使用

c

uint8_t testValue __attribute__ ((at (SRAM_BASE_ADDR + 40)));

//在创建变量的同时指定创建的地址SDRAM

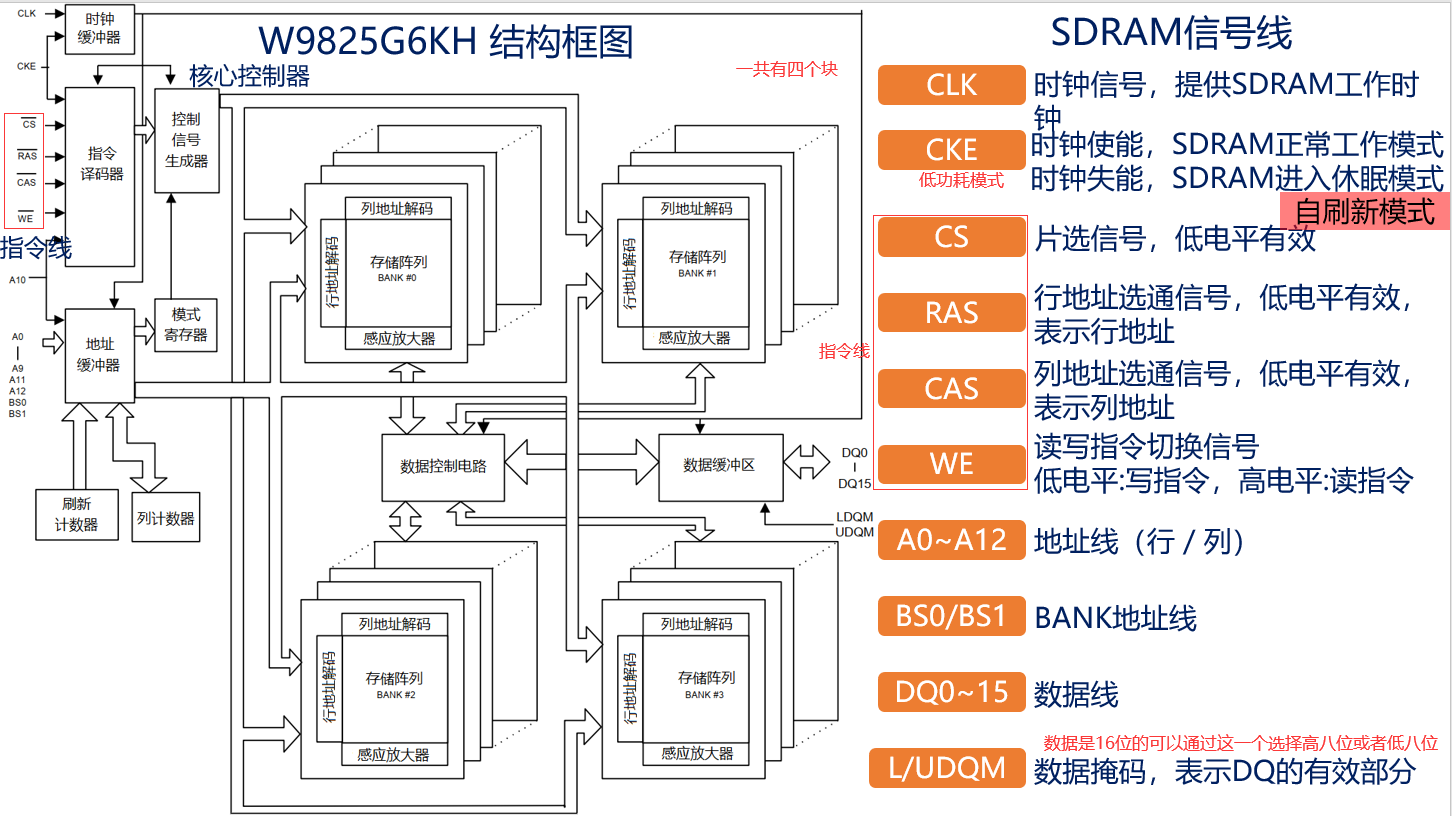

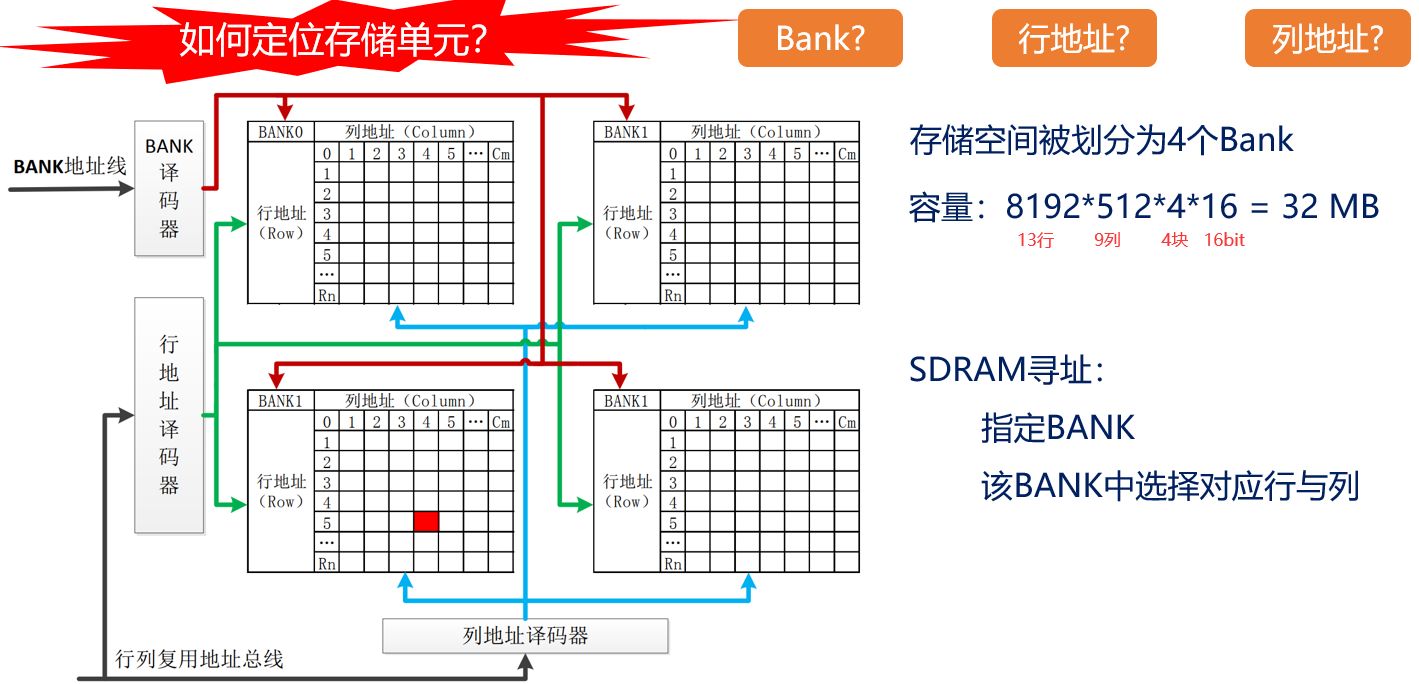

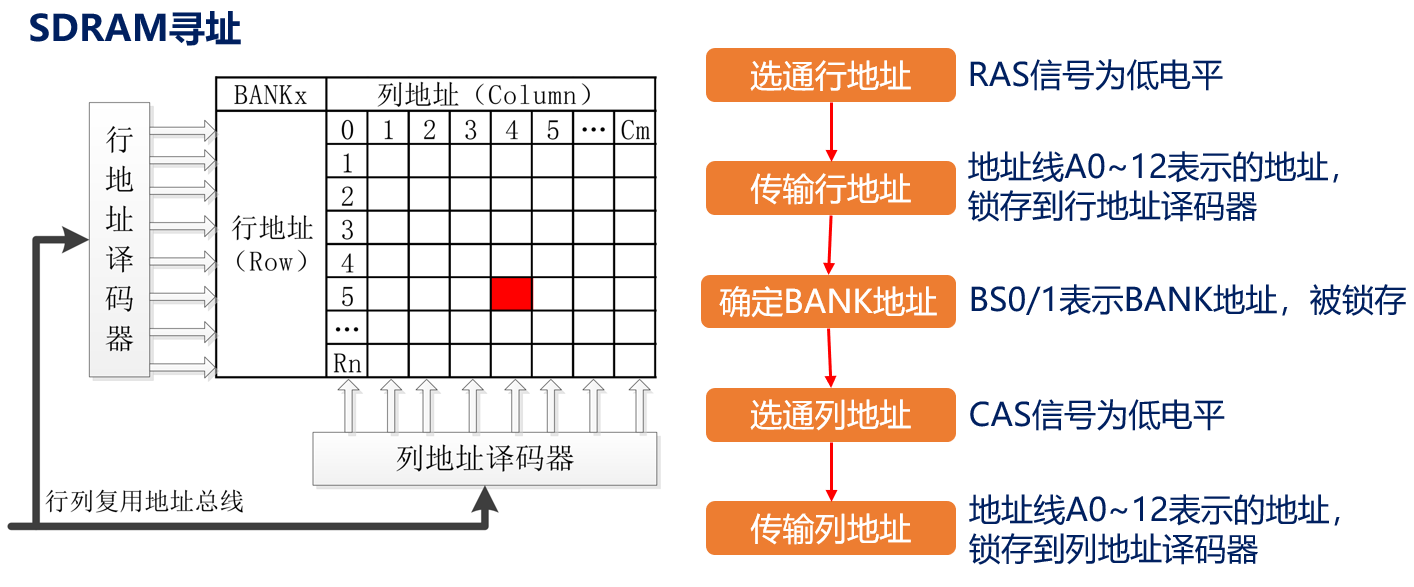

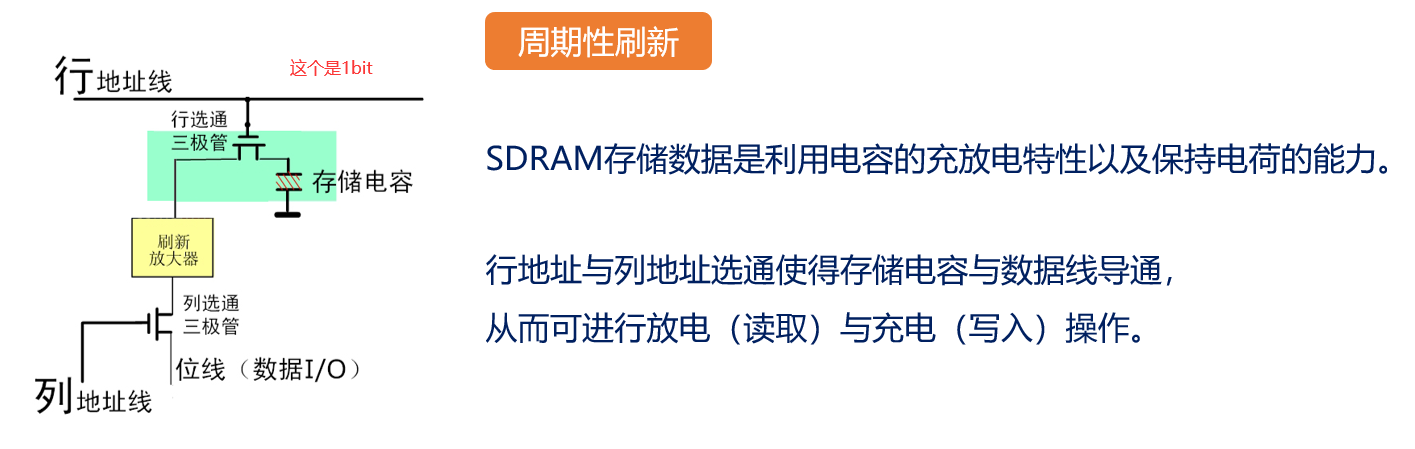

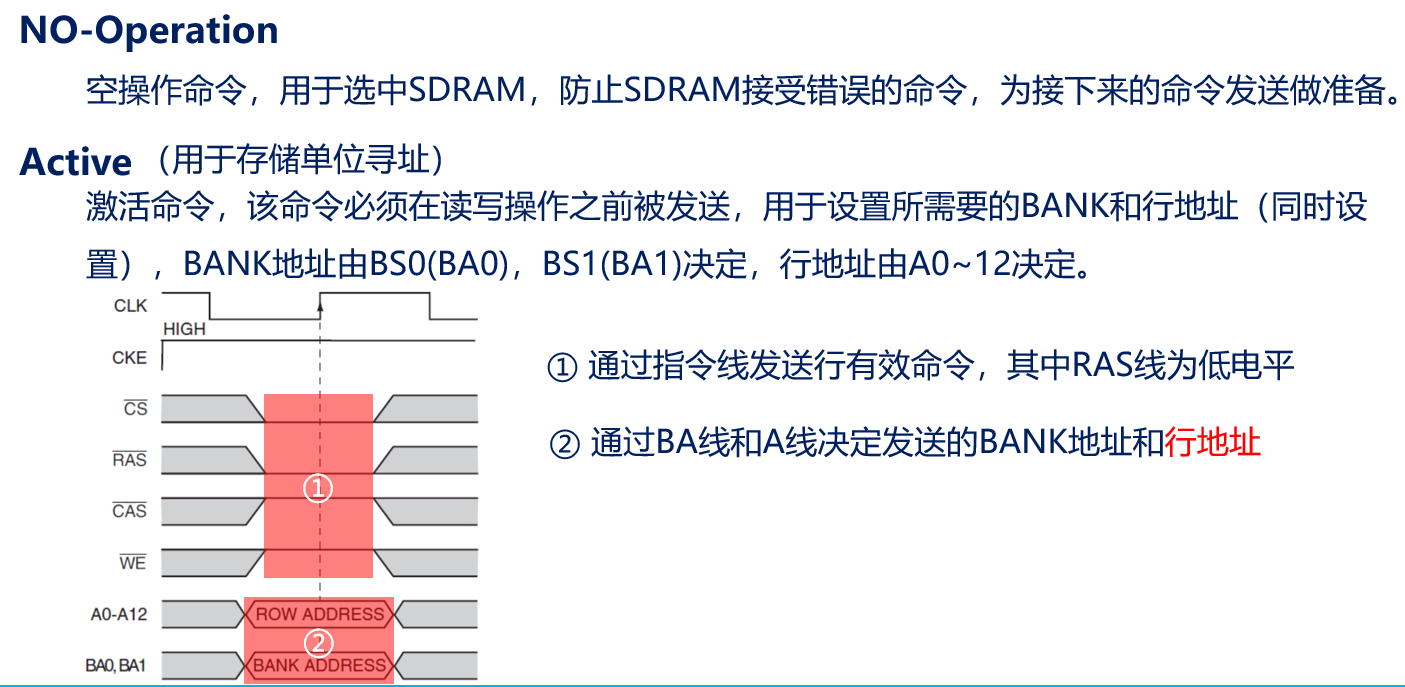

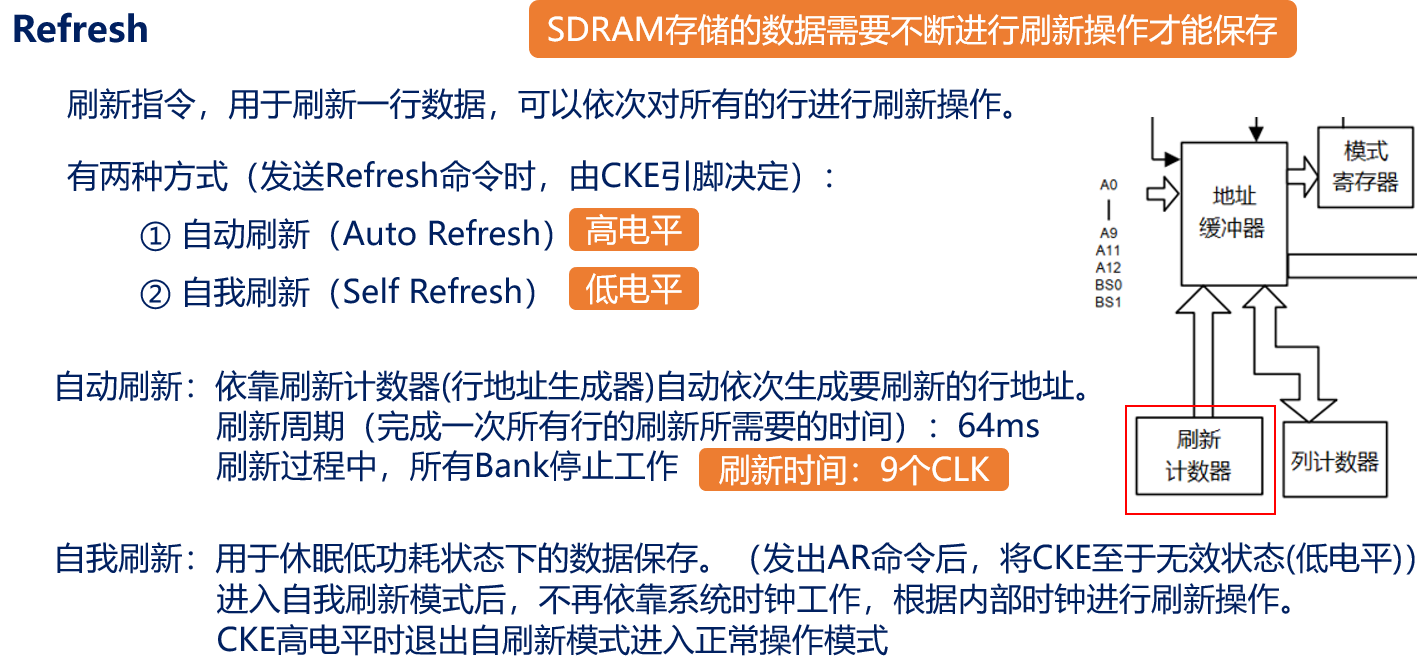

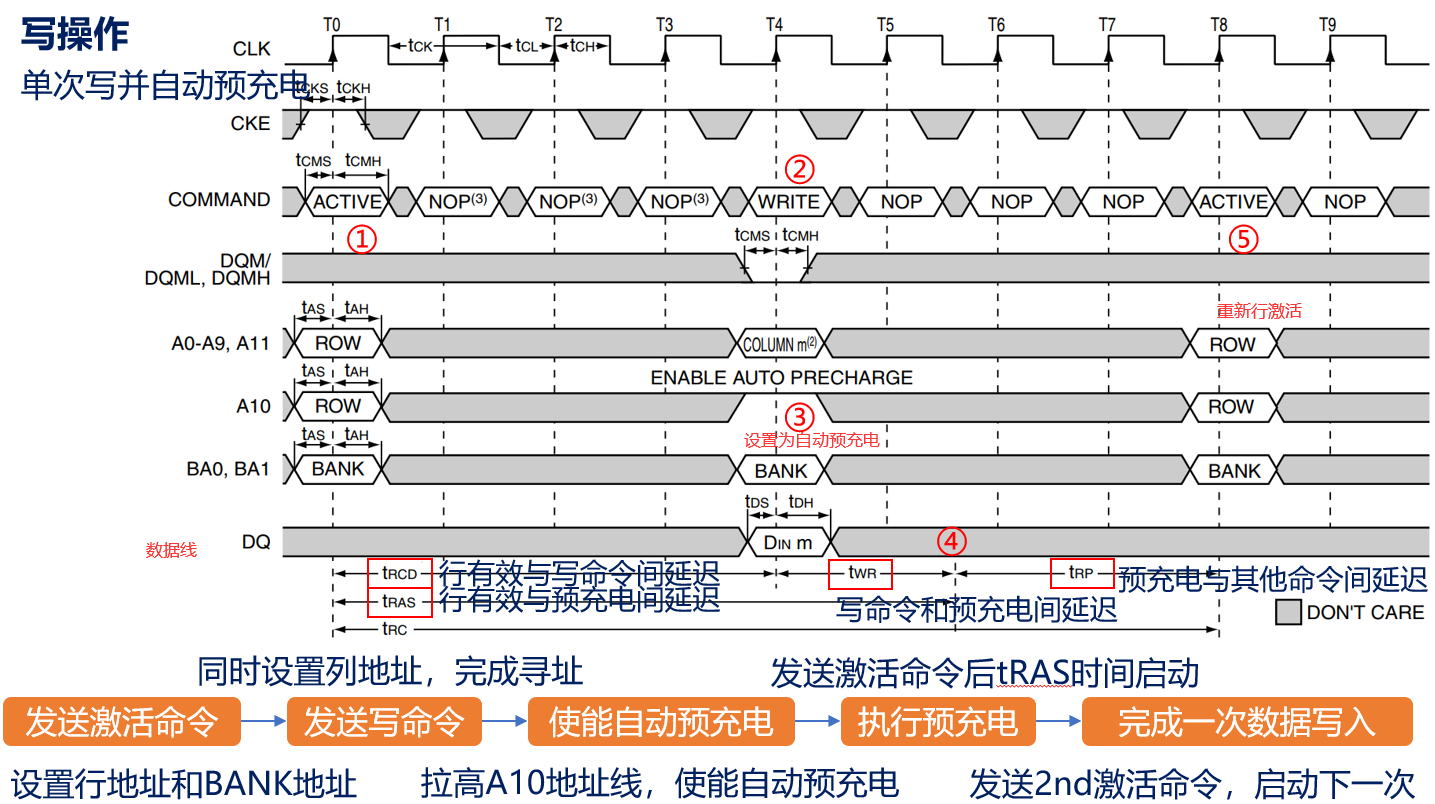

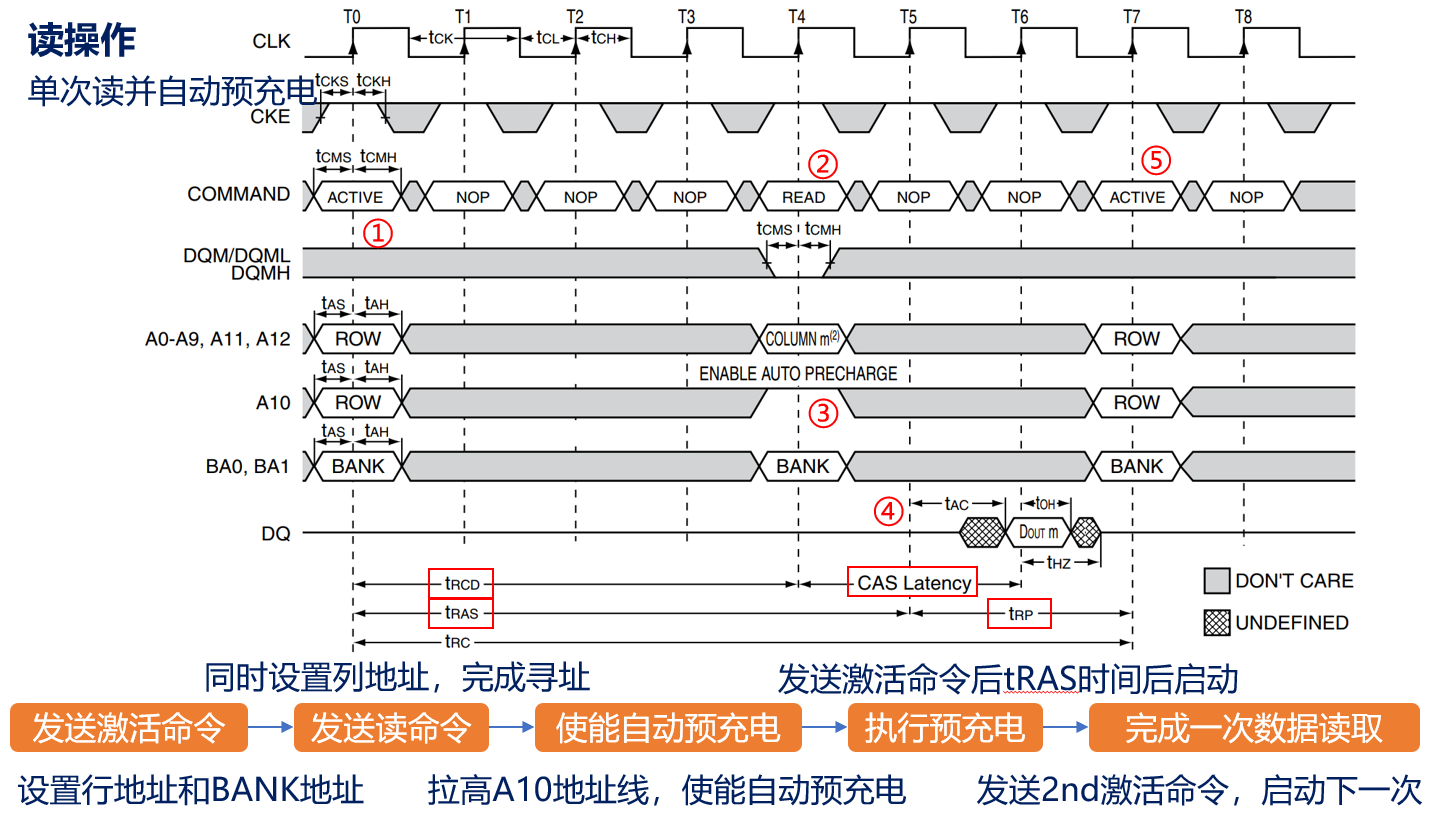

同步: 内部的工作需要同步时钟

动态: 需要不断刷新来保存数据不会丢失

随机: 数据不是线性依次存储的, 可以自由的进行数据的读写

优点, 容量比较大, 读写的速度快, 但是控制逻辑复杂

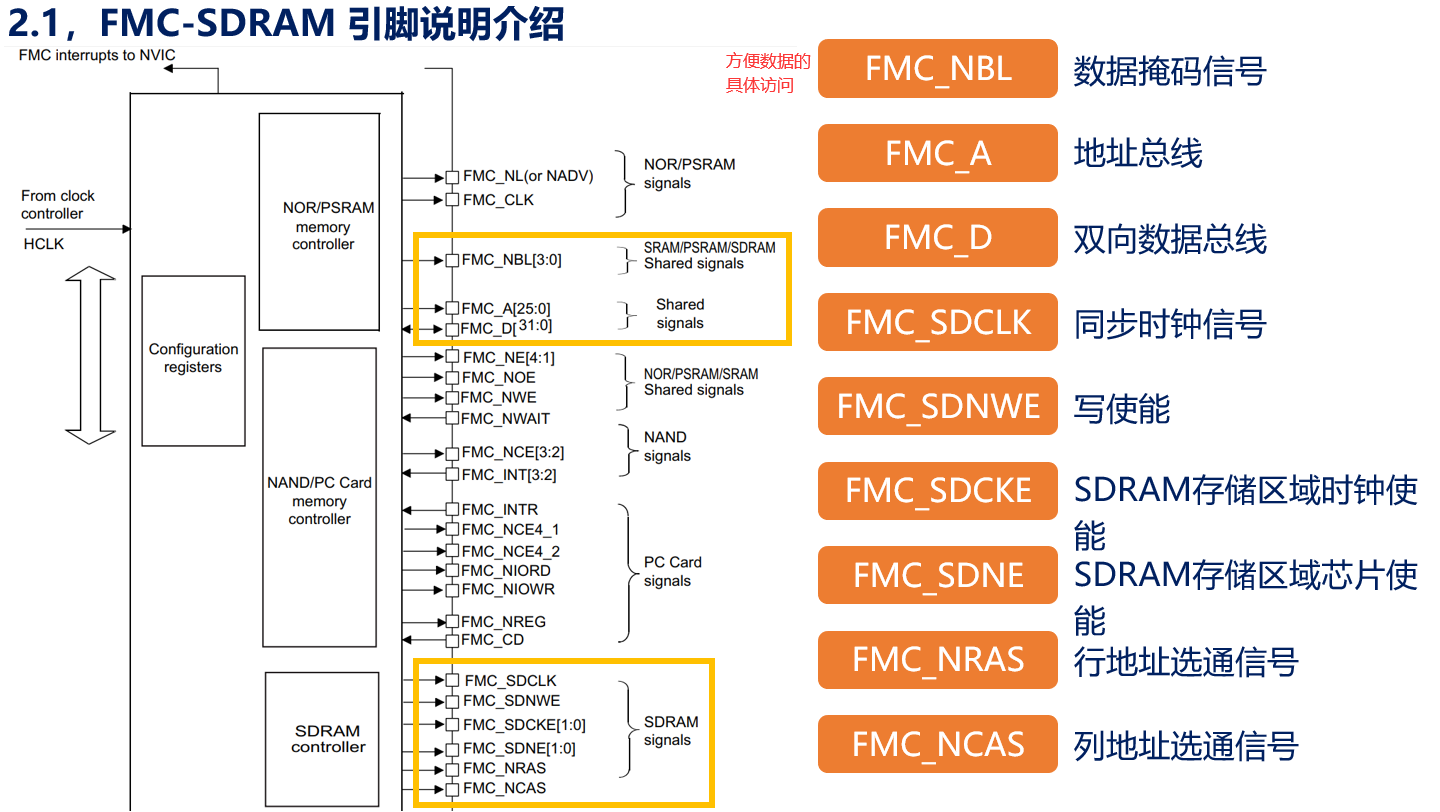

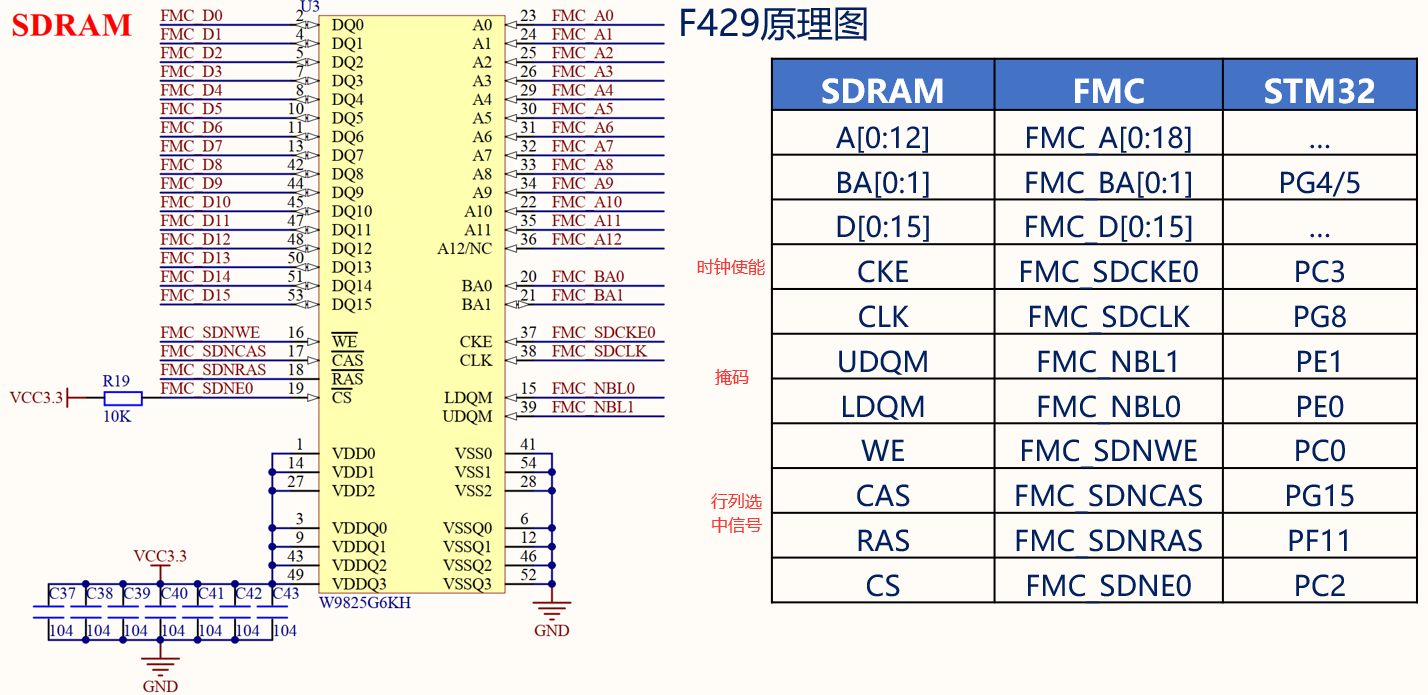

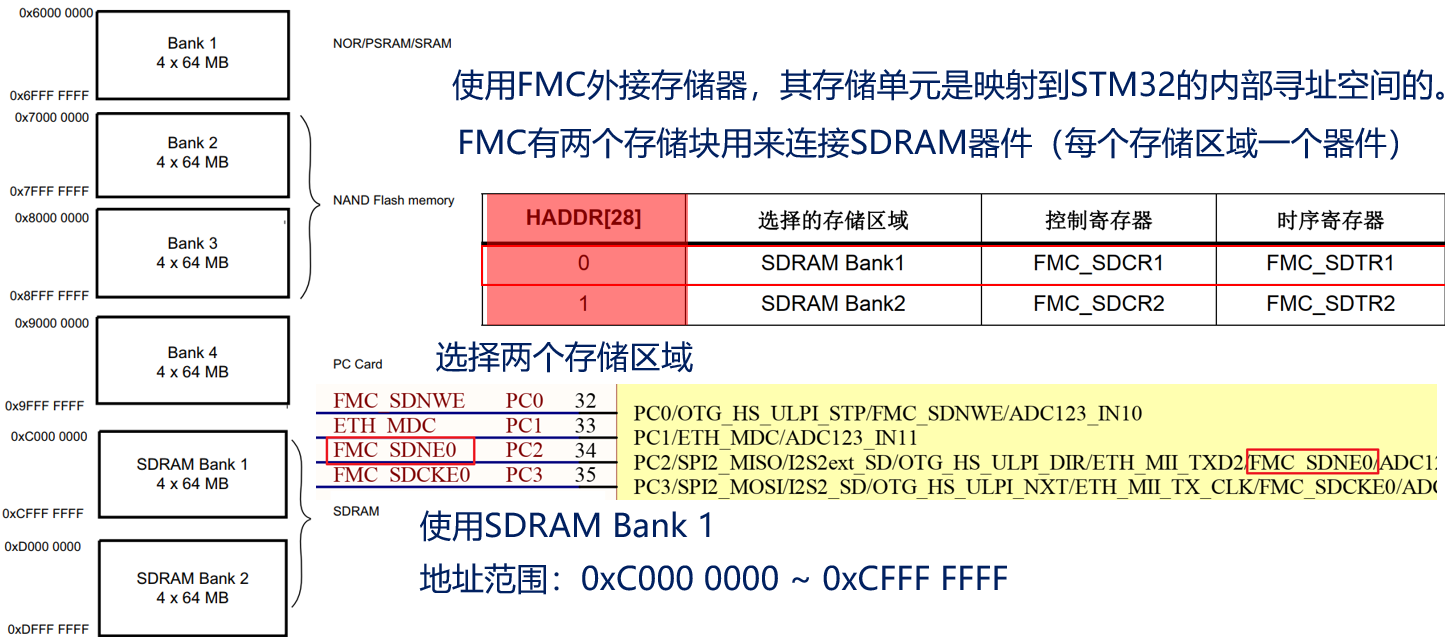

FMC

灵活的存储控制器, 可以驱动SRAM/NOR/NAND Flash以及SDRAM等存储器

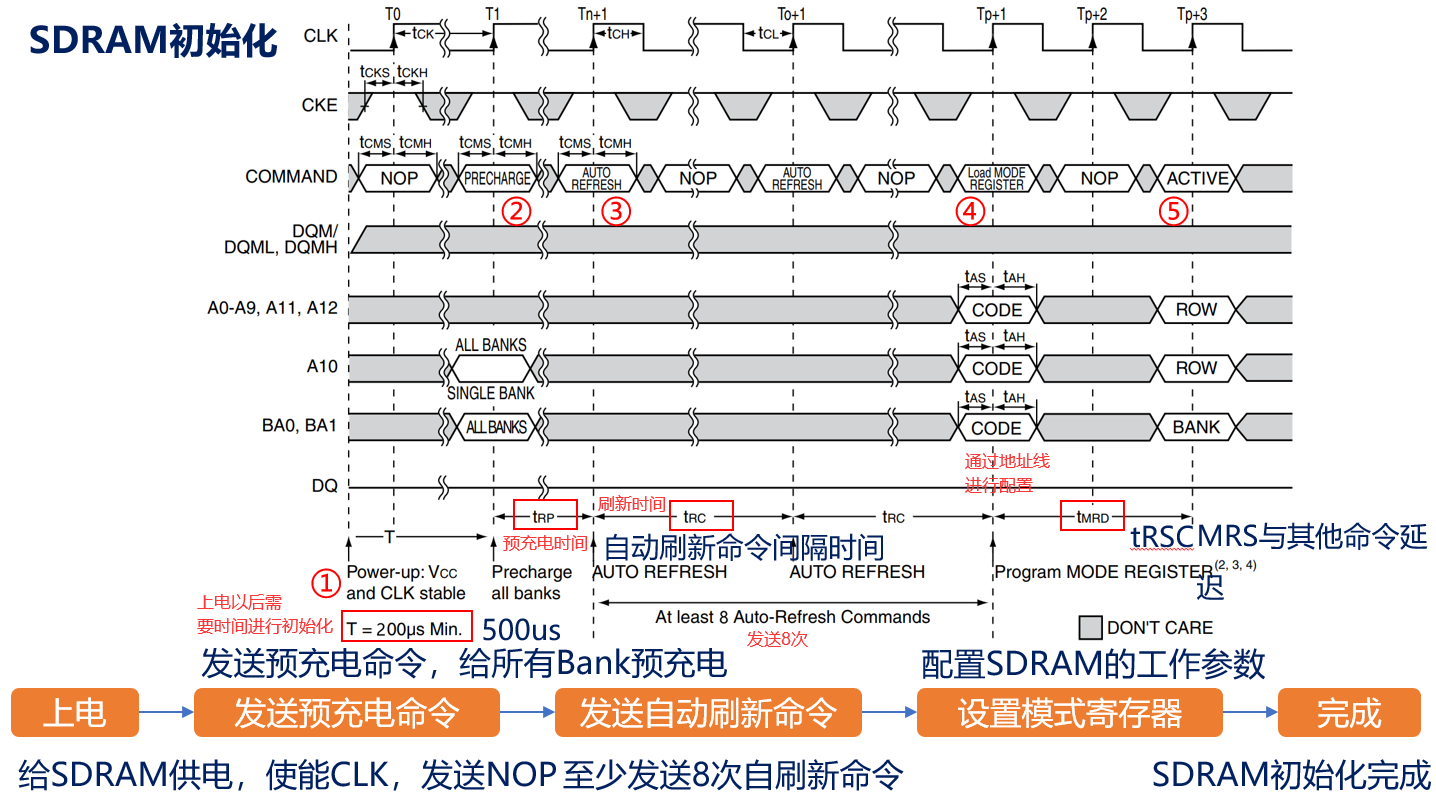

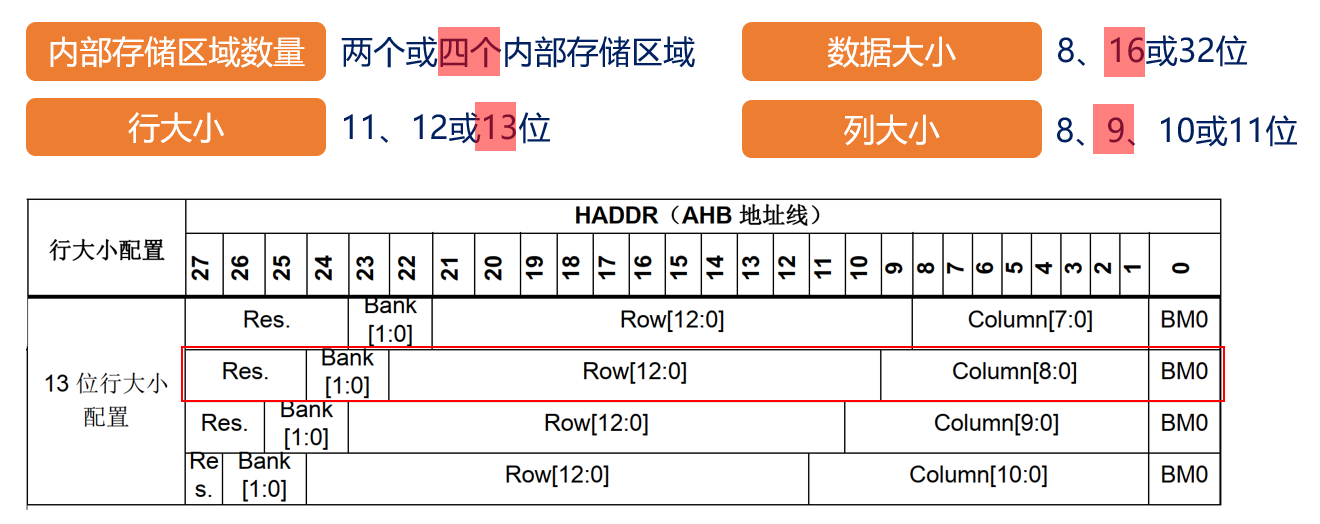

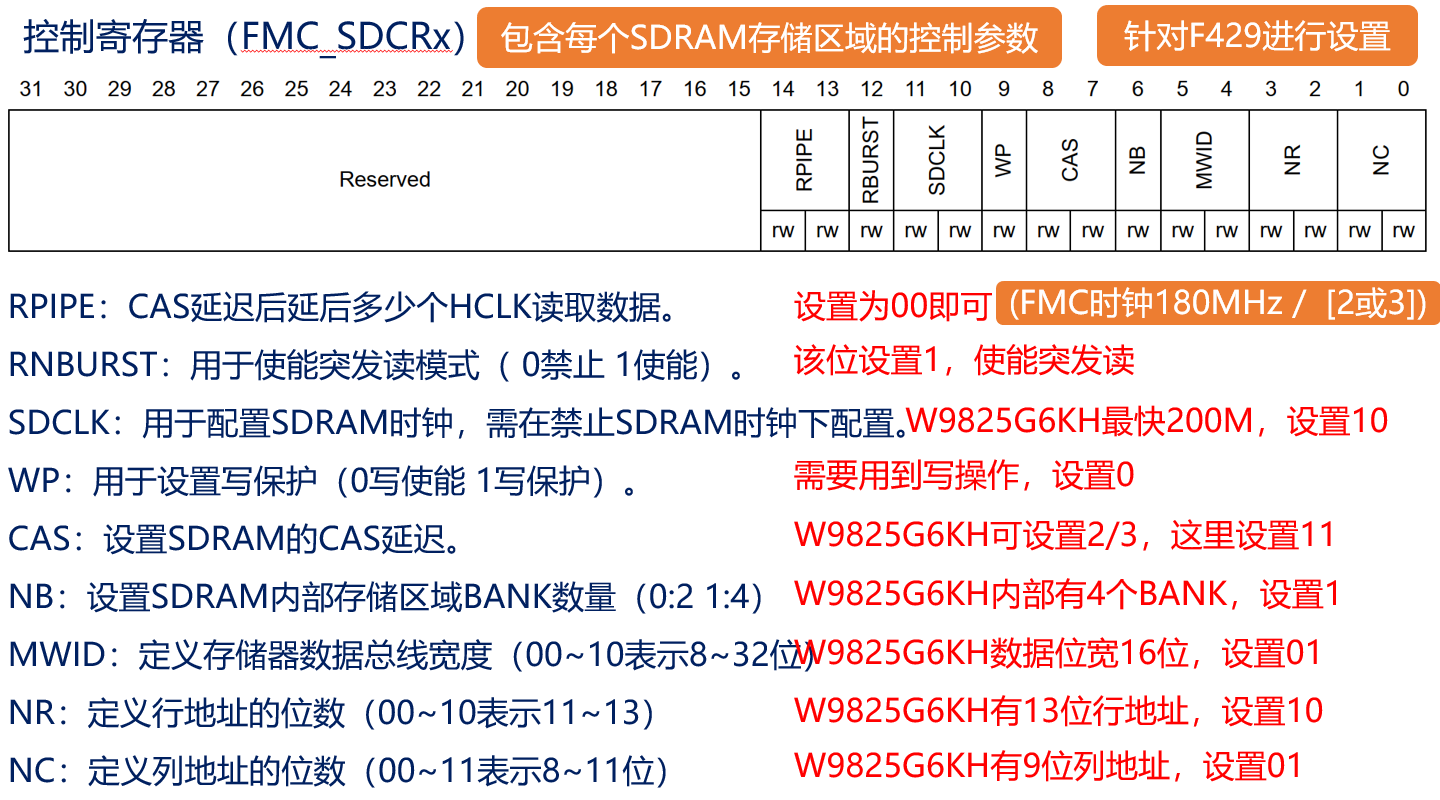

特点: 有两个存储区域, 可以独立配置, 支持8/16/32位数据总宽度, 支持13位行地址, 11位列地址, 4个内部存储区域, 支持字,半字,字节访问, 自动进行存储区域边界管理, 多存储区域乒乓访问, 支持自动刷新, 可以编程刷新变成速度, 读FIFO可以进行缓存

需要进行对应的配置, 从而获取到具体访问的数据

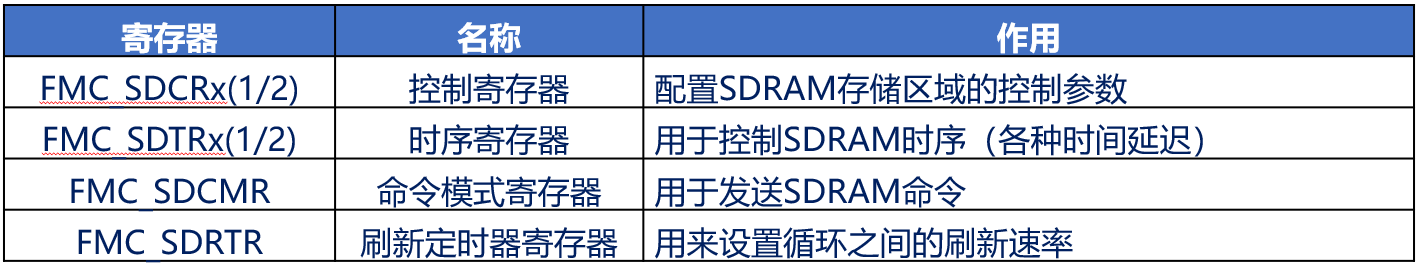

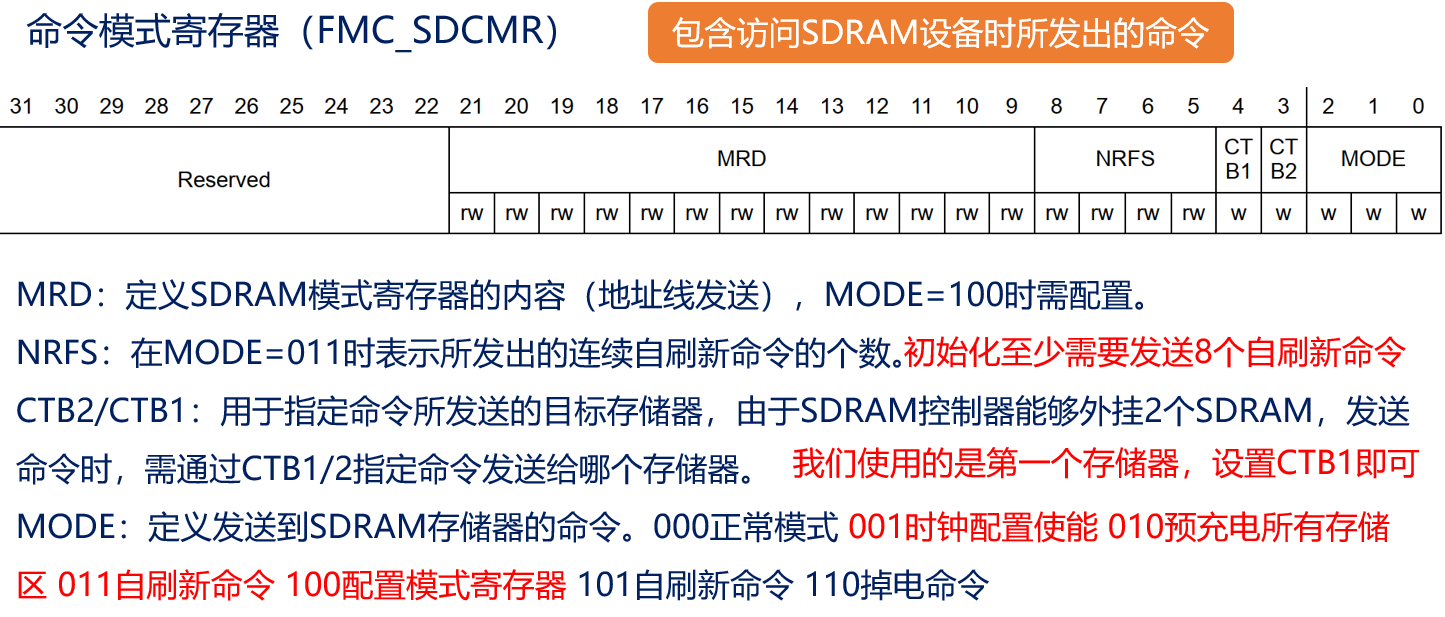

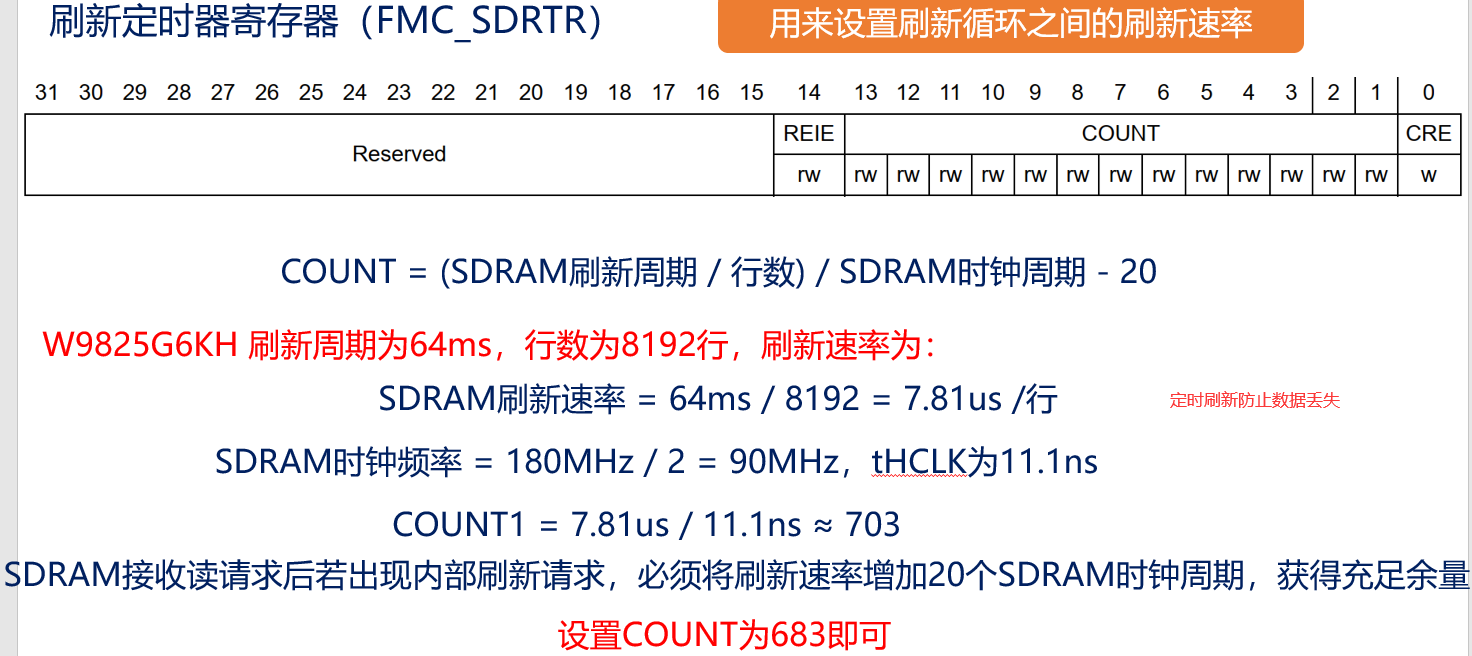

寄存器

相当于一个递减的计数器,计数到0的时候会进行刷机新